Верифікація VHDL моделей

Верифікація VHDL-моделей (англ. verification of VHDL-models) — це процес доказу того, що вона відповідає його специфікації. Верифікація передбачає моделювання VHDL-моделі проекту, що проектується, та відтворення в ході імітаційного експерименту всіх можливих вхідних впливів та внутрішніх станів системи[1].

Процес верифікації починається з розробки тест-плану (як тестувати, якими інструментарієм, в якому порядку, граничні тести, заборонені режими та ін.). Далі треба:

- створити верифікаційну середу (testbench);

- відладка програми, що тестує та моделі об'єкта;

- профілювання (виявлення і по можливості усунення ділянок тесту, що сильно знижують швидкодію);

- проведення регресійних експериментів.

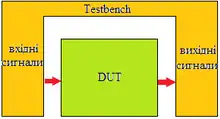

Структура тестового стенду

Інтерфейс тестового стенду

Тестовий стенд VHDL (Testbench) – це просто інша специфікація, яка складається з інтерфейсу та архітектури. Але є одна важлива особливість інтерфейсу тестового стенду – він не містить портів або параметрів. Причина цього дуже проста – тестовий стенд не є реальним пристроєм або системою, що може з’єднуватись із середовищем, отже він не потребує входів або виходів. Усі значення для вхідних портів UUT описуються всередині архітектури тестового стенду як стимулятори. Виходи спостерігаються за допомогою симулятора, і відображаються у вигляді часових діаграм, або зберігаються в файлі.

Чому тестовий стенд представляється у вигляді інтерфейсу, якщо він практично є лише архітектурою? Як вказувалось вище, архітектура не може бути описана без інтерфейсу, і це правило розповсюджується також на тестові стенди.

Тестований пристрій

Система, верифікація якої буде проводитись за допомогою тестового стенду, не вимагає ніяких модифікацій, або додаткових декларацій. Завдяки цьому тестові стенди можуть бути застосовані до будь-яких VHDL-специфікацій, навіть отриманих із зовнішнього джерела. Така ситуація може мати місце, коли виконується симуляція декількох пристроїв на рівні макету. Однак ніяких модифікацій до специфікацій пристроїв не вноситься, оскільки вони проводяться на основі результатів верифікації.

Функціональний опис (HDL-код) пристрою, що тестується (Device under test, DUT) має бути реалізований в архітектурі тестового стенду. Це виконується так само, як і в будь-якій структурній специфікації – або шляхом прямої реалізації, або шляхом реалізації компонента з декларацією компонента і конфігурацією. Портам DUT присвоюються сигнали стимулятори.

Як процеси, так і реалізації компонентів є паралельними операторами, отже немає значення, що буде виконано раніше – реалізація DUT чи визначення стимуляторів в архітектурі тестового стенду.

Стимулятори сигналів

Ядром кожного тестового стенду є набір стимуляторів – послідовність значень для кожного вхідного сигналу DUT, прив’язаних до часу. Оскільки тестовий стенд не з’єднується із середовищем за допомогою сигналів, всі стимулятори мають бути задекларовані всередині архітектури тестового стенду. Вони декларуються так само, як будь-які інші сигнали в декларативній частині архітектури. Стимулятори можуть бути описані як паралельні присвоєння сигналів (із вхідними сигналами, зміни яких описуються як часові діаграми), або в процесах, що містять присвоєння сигналів, розділених операторами wait for, за допомогою яких задаються затримки між послідовними присвоєннями сигналів. В другому випадку в якості останнього оператора процесу вказується пустий (безумовний) оператор wait. Це приводить до припинення симуляції (в протилежному випадку вона знову почнеться з початку процесу).

Оператор повідомлення

Останній елемент успішної верифікації пристрою – отримання результатів симуляції або результатів сигналізації. Їх можна отримати декількома шляхами, використовуючи вбудовані засоби симулятора, такі як відображення списку значень сигналів із зазначеними моментами змін або часових діаграм, запис в файл логів завершеної симуляції, або використання VHDL-оператора assert-report.

Останній варіант легко реалізується і використовується для відображення повідомлення, коли щось відбувається неправильно. Якщо він використовується і не відображається ніяких повідомлень протягом симуляції, можна вважати, що DUT працює, як і очікувалось.

Оператор assert-report складається з трьох елементів:

- оператора assert (перевіряє логічну умову),

- оператора report (визначає повідомлення, що буде відображено, якщо умова не виконується),

- оператора severity (інформує симулятор, наскільки серйозною є помилка – від загального зауваження до системної помилки і має перечислимий тип: NOTE, WARNING, ERROR, FAILURE).

Джерела інформації

- Поляков, А. К. (2003). Мови VHDL і Verilog в проектуванні цифрової апаратури (російська). М.: СОЛОН-Пресс. с. 320.