Фізична верифікація

Фізи́чна переві́рка (верифіка́ція) - стадія проектування ІС, на якому перевіряється топологія за допомогою програмного забезпечення EDA (Electronic design automation) на відповідність певним критеріям. Перевірка включає в себе:

- DRC (Design Rule Check - на відповідність КТО),

- LVS (Layout versus schematic - на відповідність схемі),

- ERC (Electrical Rule Check - на відповідність електричним обмеженням),

- XOR (відстеження змін), і

- Antenna Checks (перевірки на "Антенний ефект").

DRC - Правила проектування

Правила розробки (конструктивно-технологічні обмеження, КТО) містять ряд параметрів, наданих виробниками напівпровідників, які дозволяють проектувальнику перевірити правильність набору масок. Правила проектування є специфічними для конкретного процесу виробництва напівпровідників. Топологічні правила визначають деякі геометричні обмеження і умови контактування для забезпечення достатнього запасу при коливаннях у процесах виробництва напівпровідників, з тим щоб забезпечити правильне функціонування більшості елементів.

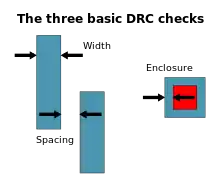

Самі основні правила проектування показано на малюнку справа. Перші являють собою єдині правила шару:

- мінімальна ширина (width) будь-якої форми в дизайні;

- мінімальна відстань між двома сусідніми об'єктами.

Ці правила існують для кожного шару напівпровідникового виробничого процесу, з найнижчих шарів з найменшим значенням (зазвичай 100 нм на 2007 рік) до верхнього шару металізації, що має більшу норму (можливо, 400 нм на 2007р.).

Двошарове правило визначає відносини, які повинні існувати між двома шарами. Наприклад, правило перекриття (enclosure) може вказати, що об'єкт одного типу, такого як контакт або міжшарове з'єднання, повинен бути покритий, з деяким запасом, металевим шаром. Типове значення в 2007 році - близько 10 нм.

Є багато інших типів правил, не показаних тут. Правило "Мінімальна площа" саме те, що випливає з назви. Правила "Антенний ефект" - складні правила, які перевіряють відносини площ кожного шару топології для конфігурацій, які можуть призвести до проблем, коли проміжні шари будуть стравлені. Існує багато інших подібних правил, докладно описаних в документації, яку надає виробник напівпровідників.

Програмне забезпечення DRC

Основна мета модуля DRC є досягнення високої загальної прибутковості і надійності топології. Якщо правила проектування порушуються, дизайн не може бути функціональним. Для поліпшення виходу придатних кристалів, DRC перетворився з простого засобу виміру і логічних перевірок, в більш складний, який змінює існуючі параметри, вводить нові, і перевіряє весь дизайн на такі обмеження, як щільність шару. Завершена топологія дає не тільки геометричне представлення дизайну, але і дані, які можуть бути корисними при виготовленні. DRC дає можливість переконатися, що структура відповідає процесу обмеження для даного типу конструкції та технологічному процесу. Тим не менш, це не гарантує, що топологія дійсно являє собою схему, яку ви хочете виготовити. Ось де використовується перевірка LVS .

LVS

Модуль LVS відповідає за відновлення принципової електричної схеми з топологічного представлення та порівняння отриманих результатів з вихідним описом електричної схеми. При відновленні електричної схеми вирішуються завдання ідентифікації компонентів електричної схеми і з'єднань, визначення їх параметрів.

Правила, на підставі яких проводиться аналіз топологічних даних і екстракція компонентів, описуються за допомогою мови SVRF (Standard Verification Rules Format). Синтаксис цієї мови дозволяє описати всі необхідні типи компонентів (3 -, 4 - і N-полярні компоненти цифрових, аналогових та СВЧ-схем) і в сукупності зі спеціальними методами екстракції забезпечує їх надійне розпізнавання в топологічному поданні.

Крім виділення самих компонентів, система дозволяє на підставі геометричних даних розрахувати їх реальні параметри і порівняти з параметрами, використаними у вихідній електричній схемі. Причому розробник може задати власні нестандартні функції розрахунку параметрів по геометричних даних. Цей модуль працює як з ієрархічними, так і з однорівневими проектами, також є засоби розпізнавання повторюваних логічних елементів і елементів пам'яті (використання цієї інформації значно підвищує продуктивність процесу верифікації). Механізм автоматичної локалізації найкоротших шляхів між неузгодженими ділянками одного кола вносить значний внесок у прискорення процесу відновлення електричної схеми.[1]

XOR перевірки

Ця перевірка зазвичай виконується після маніпуляцій з шаром металізації, коли порівнюються оригінал і зміна бази даних. Це робиться для підтвердження, що бажані зміни були зроблені, а небажані зміни не були випадково внесені. Цей крок передбачає порівняння геометричних елементів топологій двох макетів бази даних (в форматі GDS) алгоритмом XOR. В результаті перевірки бази даних матимемо всі невідповідності геометрії які є в макетах.

Перевірка на "Антенний ефект"

"Антенний ефект» виникає під час технологічних процесів плазмового травлення і виявляється в накопиченні статичного заряду на провідниках, який може привести до пробою підзатворного діелектрика МОН-транзисторів. Антенним ефект називають через велику площу полікремнію, що діє як антена для збирання заряду, який потім тече по підзатворному діелектрику. Щоб мінімізувати "антенний ефект", вводять спеціальні обмеження на площу з'єднань на внутрішніх шарах металізації. Іншим способом усунення ефекту є додавання металевих перемичок (англ. jumper), приєднаних до полікремнію.

ERC

Перевірка електричних вимог включає в себе перевірку всіх електричних з'єднань, які вважаються небезпечними. Це може включати в себе перевірку:

- легованих областей і підкладки на правильність контактів і допустимі відстані, забезпечуючи тим самим правильне живлення і заземлення;

- непідключених входів або коротке замикання виходів;

- вентилів, підключених безпосередньо до живлення.

ERC перевірки засновані на припущеннях про нормальні умови роботи ASIC, так що вони можуть дати безліч помилкових попереджень при декількох (або негативних) напругах живлення. Можлива також перевірка структур, сприйнятливих до пошкодження електростатичним розрядом (англ. ESD).

Примітки

- А. Лохов. Главный калибр компании Mentor Graphics. Электроника: Наука, Технология, Бизнес, 2/2006, с. 64-68.

Див. також

- Design rule checking