FB-DIMM

Fully Buffered DIMM, FB-DIMM (Повністю буферизована DIMM) — стандарт комп'ютерної пам'яті, який використовується для підвищення надійності, швидкості, і щільності підсистеми пам'яті. У традиційних стандартах пам'яті лінії даних підключаються від контролера пам'яті безпосередньо до ліній даних кожного модуля DRAM (іноді через буферні регістри, по одній мікросхемі регістра на 1-2 чипа пам'яті). Із збільшенням ширини каналу або швидкості передачі даних, якість сигналу на шині погіршується, ускладнюється розводка шини. Це обмежує швидкість і щільність пам'яті. FB-DIMM використовує інший підхід для вирішення цих проблем. Це подальший розвиток ідеї registered модулів — Advanced Memory Buffer здійснює буферизацію не тільки сигналів адреси, але й даних, і використовує послідовну шину до контролера пам'яті замість паралельної.

Специфікації FB-DIMM, як і інші стандарти пам'яті, опубліковані JEDEC. FB-DIMM була реалізована тільки для чипів DDR2 SDRAM.

Технологія

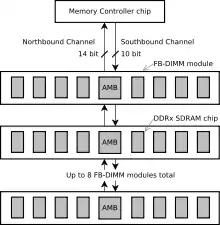

Архітектура Fully Buffered DIMM вводить нову мікросхему Advanced Memory Buffer (AMB), розташовану між контролером пам'яті і чипами DRAM. На відміну від паралельної шини, використовуваної в традиційних системах DRAM-пам'яті, в FB-DIMM використовується послідовна шина між контролером пам'яті і AMB[1]. Так досягається збільшення «ширини» (канальності) пам'яті без надмірного збільшення кількості контактів контролера пам'яті. В архітектурі FB-DIMM контролер пам'яті не займається безпосереднім записом в чипи пам'яті; ця функція перенесена в AMB. У цьому чипі відбувається регенерація і буферизація сигналів. На додаток AMB реалізує виявлення і корекцію помилок. З іншого боку, наявність AMB з проміжним буфером збільшує латентність.

Використовується пакетний протокол, кадри можуть містити дані і команди. Серед команд можна виділити команди DRAM (активація рядка — RAS, читання шпальти — CAS, оновлення — REF та ін), команди управління каналом (наприклад, запис в конфігураційні регістри), команди синхронізації. Канали зв'язку несиметричні і однонаправлені, від основного контролера пам'яті йде канал шириною 10 біт (10 диф. пар) для команд і для даних, до нього шириною 14 біт — для даних і для статусних повідомлень. AMB чипи одного каналу пам'яті організовуються в ланки, тобто шина від контролера пам'яті йде на перший AMB каналу. Кожен наступний AMB підключається за принципом точка-точка до попереднього.

Канал FB-DIMM працює на частоті, в 6 разів більшої частоти DIMM, наприклад для FB-DIMM на базі чипів пам'яті DDR2-533 (частота 533 МГц) диференційний канал працюватиме на частоті 3,2 ГГц. Для передачі одного кадру потрібно 12 циклів шини. Розмір кадру від контролера пам'яті до AMB дорівнює 120 бітам, розмір кадру від AMB дорівнює 168 бітам. Кадри містять CRC і заголовок.