Інвертор (логічний вентиль)

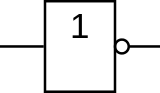

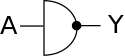

Інве́ртор, вентиль НЕ (англ. NOT gate) — логічний вентиль, який реалізує логічне заперечення. Таблиця істинності такого елемента показана справа.

| НЕ (NOT) | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| Позначення на схемах | |||||||||

| |||||||||

| Таблиця істинності | |||||||||

| |||||||||

Умовні позначення

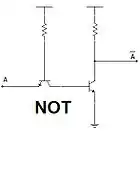

Існує два основних умовних графічних позначень вентиля НЕ на принципових схемах, описані в стандартах IEC 60617-12:1997 і ANSI 91-1984. Стандарт DIN 40700 застарів, але описані в ньому символи досі зустрічаються у схемах. Позначення логічних вентилів згідно ДСТУ ГОСТ 2.743-91 «Позначення умовні графічні в схемах. Елементи цифрової техніки» (частина ЄСКД) мають незначні відмінності від стандарту IEC 60617-12.

| IEC 60617-12:1997 | ANSI 91-1984 | DIN 40700 (до 1976) |

|---|---|---|

|

|

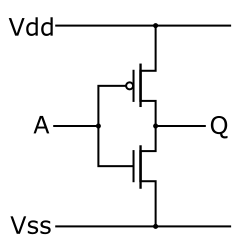

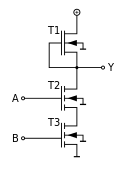

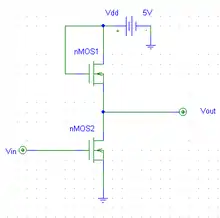

Схемотехнічна реалізація

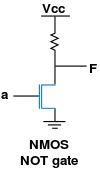

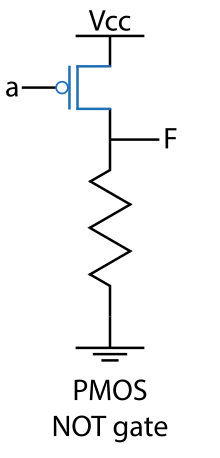

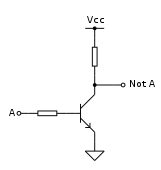

Інверторна схема видає на виході напругу, що дорівнює протилежному логічному рівню на вході. Інвертори можуть бути побудовані з використанням одного NMOS або одного PMOS транзистора з резистором.

Інвертор на N-МОН (NMOS) логіці

Інвертор на N-МОН (NMOS) логіці Інвертор на PMOS

Інвертор на PMOS Static CMOS inverter

Static CMOS inverter Інвертор на транзисторно-транзисторній логіці (ТТЛ)

Інвертор на транзисторно-транзисторній логіці (ТТЛ) Depletion-load NMOS logic NAND

Depletion-load NMOS logic NAND Saturated-load NMOS inverter

Saturated-load NMOS inverter Інвертор на резисторно-транзисторній логіці (РТЛ)

Інвертор на резисторно-транзисторній логіці (РТЛ)

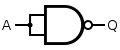

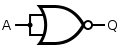

Реалізація у базисах І-НЕ та АБО-НЕ

Логічий елемент НЕ можна реалізувати в «універсальних» логічних базисах І-НЕ та АБО-НЕ:

| І-НЕ | АБО-НЕ |

|---|---|

|  |

Див. також

Посилання

- The Not Gate (англ.)

- Документація на мікросхему HEF4049B (6 інверторів, технологія КМОП) фірми NXP Semiconductors

- Документація на мікросхему SN74AS04 (6 інверторів, технологія ТТЛШ) фірми Texas Instruments