Крутість прохідної характеристики у допороговій зоні

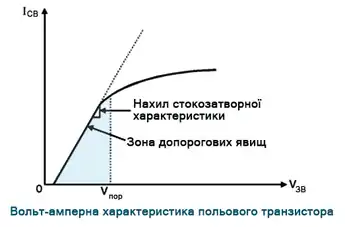

Крутість стокозатворної (прохідної) характеристики у допороговій зоні (англ. Subthreshold slope) є специфічною характеристикою вольт-амперної залежності польового МДН транзистора (англ. MOSFET).

У моделі MOSFET передбачалося, що струм протікає через канал транзистора лише тоді, коли напруга затвор-витік перевищує певне порогове значення . Насправді струм тече навіть тоді, коли нижче порогової напруги, але він на порядок слабший, ніж струми при сильній інверсії. Інверсійний шар, який спостерігається при сильній інверсії, у цьому випадку ледь видно, і цей режим також можна назвати слабкою інверсією. Тобто, підпорогова зона - це зона

У підпороговій зоні струм витоку , хоч і контролюється затвором, веде себе подібно до струму діода у прямому включенні - експоненційно зростає . Тому графік залежності струму витоку від напруги затвора при сталій напрузі стоку-витоку буде демонструвати приблизно лінійну залежність. Її нахил - це і є крутість прохідної характеристики.

Крутість прохідної характеристики у допороговій зоні є зворотньою функцією допорогового розмаху (англ. Subthreshold swing) Ss-th, яке зазвичай визначається як: [1]

- ємність ізольованого затвору (gate-oxide capacitance);

- термальна напруга;

Мінімум цієї функції можна знайти, наблизивши та / або , як результат отримаємо (термоіонна межа) 60 мВ/декаду при кімнатній температурі (300 К). Типове експериментальне значення для масштабованого MOSFET при кімнатній температурі становить ~ 70 мВ/дек, незначно деградуючи завдяки короткоканальним ефектам. [2]

Дек (декада) відповідає 10-кратному збільшення струму стоку .

Пристрій, що має крутішу прохідну характеристику, демонструє більш швидкий перехід між вимкненим (струмом незначний) та відкритим станом.

Список літератури

- Physics of Semiconductor Devices, S. M. Sze. New York: Wiley, 3rd ed., with Kwok K. Ng, 2007, chapter 6.2.4, p. 315, ISBN 978-0-471-14323-9.

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V. та ін. (2012). A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. 2012 Symposium on VLSI Technology (VLSIT). с. 131. ISBN 978-1-4673-0847-2. doi:10.1109/VLSIT.2012.6242496.

Посилання

- Оптимізація CMOS-транзисторів наднизької потужності ; Майкл Стокінгер, 2000 (англ.)

- Відеолекція порогова напруга польового транзистора на YouTube(англ.)

- Детальне пояснення про порогову напругу у відеолекції на YouTube(англ.)

- Просте пояснення процесів у допороговій зоні на YouTube(англ.)

- Відеолекція про крутість стокозатворної характеристики у допороговій зоні на YouTube(англ.)

- Уроки по електроніці. Прохідна характеристика у допороговій зоні. (англ.).