Метастабільність (електроніка)

Метастабільний стан в електроніці — можливість системи цифрової електроніки знаходитися в стані нестабільної рівноваги або метастабільному стані протягом необмеженого часу.[1] У схемах цифрової логіки, необхідно аби цифровий сигнал знаходився в певних межах значень напруги і струму, аби коректно відображати логічний рівень '0' або '1' для коректного виконання операцій логіки на схемі; якщо сигнал знаходиться в межах недозволеного робочого діапазону він може викликати збій в роботі логічних елементів, до яких надходить такий сигнал. В метастабільних станах, електричний сигнал кола не може встановитися у стабільне значення '0' або '1' логічного рівня за період часу, що є необхідним для коректної роботи електричного кола. В результаті, ця схема може працювати в непередбачуваному режимі, і це може призвести до системної помилки, що іноді називають на технічному жаргоні "глюком".[2] Метастабільність є прикладом Буріданового парадоксу.

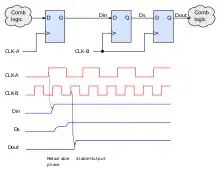

Метастабільні стани є особливістю, що притаманна асинхронним цифровим системам, і в системах, що мають більше ніж один незалежний синхросигнал з його відліком. У асинхронних системах з автоматичним таймером арбітри розроблені таким чином, що дозволяє системі тільки після того, як стан метастабільності було урегульовано, тому метастабільність є нормальним станом, а не помилкою.[3] У синхронних системах із асинхронними входами, створюються синхронізатори, які зменшують імовірність відмови до прийнятно малої.[4] Метастабільних станів можна повністю уникнути лише в повністю синхронних системах, коли виконуються умови інтервалів встановлення і утримування сигналів на входах тригерів.

Приклад

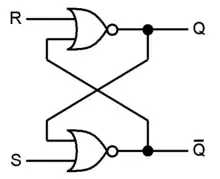

Простий приклад метастабільності виникає при роботі з RS-тригером Ні-АБО, у випадку коли обидва входи Set і Reset є істинними (тобто R=1 і S=1) і після того обидва приймають значення логічного нуля (R=0 і S=0) приблизно одночасно. Обидва виходи Q і Q початково були виставленні в 0 одночасним підняттям рівня на входах Set і Reset. Після того як обидва входи Set і Reset змінять свої значення на нуль, тригер перейде (зрештою) в один із двох стабільних станів, при якому один із виходів Q або Q буде мати на виході логічну одиницю, а інший логічний нуль. Фінальний стан буде залежати від того, хто першим із R або S повернеться до стану нуля, у хронології, але якщо два переходи відбудуться приблизно в один і той самий час, метастабільність в результаті призведе до встановлення рівня в середнє значення або до коливанням вихідних рівнів і може тривати довільно довго, до того як схема повернеться до стабільного стану.

Хоча метастабільність добре вивчена і зрозуміла, а також існує багато відомих технік для організації архітектури, що дає змогу контролювати її, вона досі залишається джерелом можливих відмов. Серйозні відмови комп'ютерів і цифрової електроніки, що були викликані метастабільними станами мають велику історію в суспільстві. Багато інженерів довгий час відмовлялися усвідомити, що бістабільні пристрої можуть входити в стан, що не є ні логічним нулем ні одиницею і існує імовірність, що він залишатиметься у невизначеному стані деякий період часу, хоча із експоненційним зменшенням цієї імовірності із плином часу.[5][6][7][8][9] Однак, метастабільність є неминучим результатом будь-якої спроби перетворити неперервний сигнал у дискретний. [10]

Арбітри

В електроніці, арбітр це спеціальна електрична схема, що визначає який із декількох сигналів надійшов першим. Арбітри використовуються в асинхронних системах аби впорядкувати дії з розрахунків із доступом до спільних ресурсів, аби уникнути існування паралельних некоректних операцій. Арбітри використовуються на входах повністю синхронних систем, а також між інтервалами синхроімпульсів, як синхронізатори вхідних сигналів. Вони можуть мінімізувати виникнення метастабільності до дуже малої імовірності, однак, всі арбітри також мають метастабільні стани, які не можливо уникнути на граничних ділянках вхідних станів, що призводять до різних виходів.[11]

Див. Також

Примітки

- Thomas J. Chaney and Charles E. Molnar (April 1973). Anomalous Behavior of Synchronizer and Arbiter Circuits. IEEE Transactions on Computers C–22 (4): 421–422. ISSN 0018-9340. doi:10.1109/T-C.1973.223730.

- Chaney, Thomas J. My Work on All Things Metastable OR Me and My Glitch. Архів оригіналу за 8 грудня 2015. Процитовано 23 січня 2019.

- John Bainbridge (2002). Asynchronous system-on-chip interconnect. Springer. с. 18. ISBN 978-1-85233-598-4.

- Chaney, Thomas J. "Reprint of Technical Memorandum No. 10, "The Glitch Phenomenon" (1966)".Washington University St. Louis, MO

- Harris, Sarah; Harris, David (2015). Digital Design and Computer Architecture: ARM Edition. Morgan Kaufmann. с. 151–153. ISBN 012800911X.

- Ginosar, Ran (2011). Metastability and Synchronizers: A tutorial. VLSI Systems Research Center. Electrical Engineering and Computer Science Dept., Technion—Israel Institute of Technology, Haifa., p. 4-6

- Xanthopoulos, Thucydides (2009). Clocking in Modern VLSI Systems. Springer Science and Business Media. с. 196. ISBN 1441902619., p. 196, 200, eq. 6-29

- A Metastability Primer (PDF). Application Note AN-219. Phillips Semiconductor. 1989. Процитовано 20 січня 2017.

- Arora, Mohit (2011). The Art of Hardware Architecture: Design Methods and Techniques for Digital Circuits. Springer Science and Business Media. ISBN 1461403979., p. 4-5, eq. 1-1

- Leslie Lamport (February 2012) [December 1984]. Buridan's Principle. Процитовано 9 липня 2010.

- Richard F. Tinder (2009). Asynchronous sequential machine design and analysis: a comprehensive development of the design and analysis of clock-independent state machines and systems. Morgan & Claypool Publishers. с. 165. ISBN 978-1-59829-689-1.

Посилання

- Metastability Performance of Clocked FIFOs

- The 'Asynchronous' Bibliography

- Asynchronous Logic

- Efficient Self-Timed Interfaces for Crossing Clock Domains

- Dr. Howard Johnson: Deliberately inducing the metastable state

- Detailed explanations and Synchronizer designs

- Metastability Bibliography

- Clock Domain Crossing: Closing the Loop on Clock Domain Functional Implementation Problems, Cadence Design Systems

- Stephenson, Jennifer. Understanding Metastability in FPGAs. Altera Corporation white paper. July 2009.

- Bahukhandi, Ashirwad. Metastability. Lecture Notes for Advanced Logic Design and Switching Theory. January 2002.

- Cummings, Clifford E. Synthesis and Scripting Techniques for Designing Multi-Asynchronous Clock Designs. SNUG 2001.

- Haseloff, Eilhard. Metastable Response in 5-V Logic Circuits. Texas Instruments Report. February 1997.

- Nystrom, Mika, and Alain J. Martin. Crossing the Synchronous Asynchronous Divide. WCED 2002.

- Patil, Girish, IFV Division, Cadence Design Systems. Clock Synchronization Issues and Static Verification Techniques. Cadence Technical Conference 2004.

- Smith, Michael John Sebastian. Application-Specific Integrated Circuits. Addison Wesley Longman, 1997, Chapter 6.4.1.

- Stein, Mike. Crossing the abyss: asynchronous signals in a synchronous world EDN design feature. July 24, 2003.

- Cox, Jerome R. and Engel, George L., Blendics, Inc. White Paper "Metastability and Fatal System Errors"] Nov. 2010

- Adam Taylor, "Wrapping One's Brain Around Metastability", EE Times, 2013-11-20