Тригер

Три́гер (англ. trigger, flip-flop) — електронна логічна схема, яка має два стійкі стани, в яких може перебувати, доки не зміняться відповідним чином сигнали керування. Напруги і струми на виході тригера можуть змінюватися стрибкоподібно. Тригер це мультивібратор із двома стабільними станами.

Загальний опис

В арифметичних і логічних пристроях для збереження інформації найчастіше використовують тригери – пристрої з двома стійкими станами по виходу, які містять елементарну запам'ятовувальну комірку (бістабільна схема БС) і схему керування (СК). Схема керування перетворює інформацію, яка надходить, на комбінацію сигналів, що діють безпосередньо на входи елементарної запам'ятовувальної комірки. Для забезпечення надійного перемикання в точках А для деяких тригерів потрібні кола затримки. З цією метою можуть використовуватися запам'ятовувальні елементи на основі БС того ж типу, що вже є у тригері. Схему такого тригера називають схемою типу M-S (master-slave), оскільки стан однієї БС, яку називають веденою, повторює стан додаткової БС, яку називають ведучою.

Тригери широко використовуються для формування імпульсів, у генераторах одиничних сигналів, для побудови подільників частоти, лічильників, перерахункових пристроїв, регістрів, суматорів, у пристроях керування тощо.

У більшості серій інтегральних елементів містяться тригери різних типів, у тому числі універсальні.

- Класифікація тригерів

- за способом організації логічних зв'язків розрізняють тригери з запуском (RS-тригери); з лічильним входом (Т-тригери); тригери затримки (D-тригери); універсальні (JK-тригери); комбіновані (наприклад, RST-, JKRS-, DRS-тригери).

- за способом запису інформації тригери поділяють на несинхронізовані (асинхронні, нетактові) і синхронізовані (тактові).

- за кількістю інформаційних входів тригери можуть бути з одним, двома та багатьма входами.

- за видом вихідних сигналів тригери поділяються на статичні і динамічні. Статичні тригери – тригери, в яких вихідні сигнали в стійких станах залишаються незмінними в часі. Динамічні тригери – тригери, в яких вихідні сигнали в стійких станах змінюються в часі.

- за способом запам'ятовування інформації тригери можуть бути з логічною і фізичною організацією пам'яті. Перші виконують на логічних елементах І, АБО, НІ, І-НІ, АБО-НІ, І-АБО-НІ і т.д., а другі є елементами запам'ятовувальних пристроїв, у яких використовують нелінійні властивості матеріалів або нелінійні вольт-амперні характеристики компонентів.

Типи тригерів

RS-тригери

RS-тригер асинхронний

| S | R | Q(t) | Q(t) | Q(t+1) | Q(t+1) |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | не визначено | не визначено |

| 1 | 1 | 1 | 0 | не визначено | не визначено |

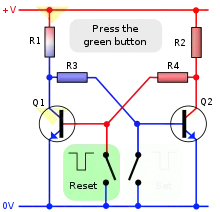

RS-тригер[1][2], або SR-тригер— тригер, який зберігає свій попередній стан при нульових входах та змінює свій вихідний стан при подачі на один з його входів одиниці.

При подачі одиниці на вхід S (від англ. Set — встановити) вихідний стан стає рівним логічної одиниці. А при подачі одиниці на вхід R (від англ. Reset — скинути) вихідний стан стає рівним логічному нулю. Стан, при якому на обидва входи R і Sодночасно подані логічні одиниці, в найпростіших реалізаціях є забороненим (оскільки вводить схему в режим генерації), в складніших реалізаціях RS-тригер переходить в третій стан QQ=00. Одночасне зняття двох «1» практично неможливе. При знятті однієї з «1» RS-тригер переходить в стан, що визначається другою «1». Таким чином RS-тригер має три стани, з яких два стійких (при знятті сигналів керування RS-тригер залишається у встановленому стані) і одне нестійке (при знятті сигналів керування RS-тригер не залишається у встановленому стані, а переходить в один з двох стійких станів).

RS-тригер використовується для створення сигналу з позитивним та негативним фронтами, окремо керованими за допомогою стробів, рознесених в часі. Також RS-тригери часто використовуються для запобігання так званого явища брязкоту контактів.

RS-тригери іноді називають RS-фіксасаторами.

Умовне графічне позначення асинхронного RS-тригера

Умовне графічне позначення асинхронного RS-тригера Логічна схема асинхронного RS-тригера на елементах 2І-НЕ

Логічна схема асинхронного RS-тригера на елементах 2І-НЕ Граф переходів асинхронного RS-тригера

Граф переходів асинхронного RS-тригера Карта Карно асинхронного RS-тригера

Карта Карно асинхронного RS-тригера Асинхронний RS-тригер на логічних елементах 2АБО-НЕ

Асинхронний RS-тригер на логічних елементах 2АБО-НЕ

RS-тригер синхронний

| C | S | R | Q(t) | Q(t+1) |

|---|---|---|---|---|

| 0 | x | x | 0 | 0 |

| 1 | 1 | |||

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | не визначено |

| 1 | 1 | 1 | 1 | не визначено |

Схема синхронного RS-тригера збігається зі схемою одноступінчастого парафазного (двофазного) D-тригера, але не навпаки, оскільки в парафазного (двофазному) D-тригері не використовуються комбінації S=0, R=0 і S=1, R=1.

Алгоритм функціонування синхронного RS-тригера можна представити формулою

де x — невизначений стан.

Умовне графічне позначення синхронного RS-тригера

Умовне графічне позначення синхронного RS-тригера Схема синхронного RS-тригера на елементах 2І-НЕ

Схема синхронного RS-тригера на елементах 2І-НЕ Граф переходів синхронного RS-тригера

Граф переходів синхронного RS-тригера Карта Карно синхронного RS-тригера

Карта Карно синхронного RS-тригера

D-тригери

D-тригери також називають тригерами затримки (від англ. Delay).

D-тригер синхронний

| D | Q(t) | Q(t+1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

D-тригер (D від англ. delay — затримка[3][4][5] або від англ. data — дані) — запам'ятовує стан входу та видає його на вихід. D-тригери мають, як мінімум, два входи: інформаційний D і синхронізації C. Після приходу активного фронту імпульсу синхронізації на вхід C D-тригер відкривається. Збереження інформації в D-тригерах відбувається після спаду імпульсу синхронізації С. Оскільки інформація на виході залишається незмінною до приходу чергового імпульсу синхронізації, D-тригер називають також тригером із запам'ятовуванням інформації або тригером-засувкою. Міркуючи чисто теоретично, парафазний (двофазний) D-тригер можна утворити з будь-яких RS- або JK-тригерів, якщо на їх входи одночасно подавати взаємно інверсні сигнали.

D-тригер переважно використовується для реалізації засувки. Наприклад, для зняття 32 біт інформації з паралельної шини, беруть 32 D-тригери і об'єднують їх входи синхронізації для керування записом інформації в засувку, а 32 входи D під'єднують до шини.

У одноступінчатих D-тригерах під час прозорості всі зміни інформації на вході D передаються на вихід Q. Там, де це небажано, потрібно застосовувати двоступеневі (двотактні, Master-Slave, MS) D-тригери.

D-тригер двоступінчастий

У одноступінчастому тригері є одна щабель запам'ятовування інформації, а в двоступінчастому — дві такі щаблі. Спочатку інформація записується в першу сходинку, а вже потім переписується у другу та з'являється на виході. Двоступінчастий тригер позначають ТТ. Двоступеневий D-тригер називають тригером з динамічним керуванням. Загальна схема двоступінчастого тригера

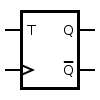

T-тригери

Т-тригер (від англ. Toggle — перемикач) часто називають рахунковим тригером, оскільки він є найпростішим лічильником до 2.

Т-тригер асинхронний

Асинхронний Т-тригер не має входу дозволу рахунку — Т і переключається по кожному тактовому імпульсу на вході С.

T-тригер синхронний

| T | Q(t) | Q(t+1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Синхронний Т-тригер[6], при одиниці на вході Т, по кожному такту на вході C змінює свій логічний стан на протилежний, і не змінює вихідний стан при нулі на вході T. Т-тригер можна побудувати на JK-тригері, на двоступінчатому (Master-Slave, MS) D-тригері і на двох одноступінчатих D-тригерах та інверторі.

Як можна бачити в таблиці істинності JK-тригера, він переходить в інверсний стан щоразу при одночасній подачі на входи J і K логічної 1. Ця властивість дозволяє створити на базі JK-тригера Т-тригер, об'єднуючи входи J і K.

У двоступінчатому (Master-Slave, MS) D-тригері інверсний вихід Q з'єднується з входом D, а на вхід C подаються лічильні імпульси. Внаслідок цього тригер при кожному рахунковому імпульсі запам'ятовує значення Q, тобто буде перемикатися в протилежний стан.

Т-тригер часто застосовують для пониження частоти в 2 рази, при цьому на Т вхід подають одиницю, а на С— сигнал з частотою, яка буде поділена на 2.

JK-тригер

| J | K | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

JK-тригер[7] [8] працює так само як RS-тригер, з одним лише винятком: при подачі логічної одиниці на обидва входи J і K стан виходу тригера змінюється на протилежне. Вхід J (від англ. Jump — стрибок) аналогічний входу S у RS-тригера. Вхід K (від англ. Kill — вбити) аналогічний входу R у RS-тригера. При подачі одиниці на вхід J і нуля на вхід K вихідний стан тригера стає рівним логічній одиниці. А при подачі одиниці на вхід K і нуля на вхід J вихідна стан тригера стає рівним логічному нулю. JK-тригер на відмінну від RS-тригера не має заборонених станів на основних входах, проте це ніяк не допомагає при порушенні правил розробки логічних схем. На практиці застосовуються лише синхронні JK-тригери, тобто стану основних входів J і K враховуються лише в момент тактування, наприклад по позитивному фронту імпульсу на вході синхронізації.

На базі JK-тригера можливо побудувати D-тригер або Т-тригер. Як можна бачити в таблиці істинності JK-тригера, він переходить в інверсний стан щоразу при одночасній подачі на входи J і K логічної 1. Ця властивість дозволяє створити на базі JK-тригера Т-тригер, об'єднавши входи J і K[9].

Алгоритм функціонування JK-тригера можна представити формулою

Умовне графічне позначення JK-тригера зі статичним входом З

Умовне графічне позначення JK-тригера зі статичним входом З Граф переходів JK-тригера

Граф переходів JK-тригера Карта Карно JK-тригера

Карта Карно JK-тригера

Особливості таймінгу

Параметри таймінгу

Вхід тригера має утримуватися в сталому значенні на період часу довкола зростаючого фронту синхроімпульсу, цей період відомий як апертура. Уявімо, що нам необхідно зробити фото жаби, що сидить на листку лілії.[10] Допустимо, потім жаба стрибає у воду. Якщо ви зробите знімок в той момент коли вона стрибає у воду, ви матимете розмите зображення жаби, що стрибає — чітко не ясно в якому стані знаходиться жаба. Але якщо ви зробите фото, доки жаба сидить спокійно на листку (або коли вона вже знаходиться спокійно у воді), ви отримаєте чітке зображення. Так само і значення тригера, воно повинно утримуватися у стійкому стані під час апертури тригера.

Час установки — мінімальна кількість часу при якому вхідний сигнал повинен утримуватися у стійкому стані перед настанням синхроімпульсу, так щоб дані могли б надійно зафіксовані імпульсом.

Час утримання — мінімальна кількість часу, при якому вхідний сигнал повинен утримуватися у стійкому стані після настання синхроімпульсу, так що дані надійно фіксуватимуться імпульсом.

Апертура — сума часу установки і часу утримання. Вхід даних повинен утримуватися у стійкому стані весь цей період часу.[10]

Час відновлення це мінімальна кількість часу коли асинхронні входи set або reset повинні залишатися неактивними перед настанням синхроімпульсу, так що дані надійно фіксуватимуться синхроімпульсом. Час відновлення для асинхронних входів set або reset таким чином є подібним до часу установки входу даних.

Час видалення це мінімальна кількість часу при якому асинхронні входи set або reset повинні залишатися неактивними після настання синхроімпульсу, так що дані можуть надійно фіксуватися синхроімпульсом. Час видалення для асинхронних входів set або reset є подібним до часу утримання входу даних.

Короткі імпульси, які застосовуються до асинхронних входів (set, reset) не повинні повністю застосовуватися в межах періоду відновлення-видалення, інакше стан тригеру стає цілком невизначеним, чи відбудеться перехід тригеру у відповідний стан. У іншому випадку, якщо асинхронний сигнал зробить один перехід стану так що він припаде на період між часом відновлення/видалення, зрештою тригер перейде до відповідного стану, але може відбутися коротко тривалий збій на виході, в залежності від вхідного синхронного сигналу. Друга ситуація може бути не мати значної важливості при розробці схеми.

Сигнали Set і Reset (а також інші) можуть бути або синхронними або асинхронними і тому вони характеризуються або часом Установки/утримання або Відновлення/видалення, а синхронність дуже залежить від реалізації тригера.

Різниця між часом Встановлення/утримання і Відновленням/видаленням часто є важливою при визначенні таймінгу великих схем, оскільки асинхронні сигнали можуть виявитися менш критичними ніж синхронні. Розрізнення цих двох понять дає можливість розробнику визначити умови верифікації для цих типів сигналів незалежно один від одного.

Метастабільність

Тригери є причиною проблеми, що називається метастабільність, яка може статися коли два входи, такі як вхід даних і синхроімпульс або синхроімпульс і reset, змінюються в приблизно один і той самий момент часу. Коли порядок не є чітко визначеним, в рамках прийнятних обмежень по таймінгу, в результаті вихід може мати непередбачувану поведінку, так що встановлення стану із одного в інший займатиме більше часу, або навіть відбуватиметься коливання значень декілька раз перш ніж вони встановляться. Теоретично, час встановлення може бути необмежений. В комп'ютерних системах, така поведінка метастабільності може призвести до пошкодження даних або до аварійного завершення програми, якщо стан не буде стійким, перед тим як інша частина кола використає це значення; зокрема, якщо два різних логічних розгалуження використовують один і той самий вихід тригера, одна частина може інтерпретувати його як 0, в той час як інша як 1, коли значення не знаходиться в стабільному стані, що приводить до виникнення невідповідного стану.[11]

Метастабільності тригерів можна уникнути, якщо бути певними, що входи даних і керування залишатимуться валідними і постійними у задані періоди до і після синхроімпульсу, що називаються часом встановлення (tsu) і часом утримання (th) відповідно. Ці інтервали визначаються у характеристиках пристрою, і як правило становлять від декількох наносекунд до декількох сотень пікосекунд. В залежності від внутрішньої організації тригера, можливо побудувати такий пристрій, що матиме нульовий (або негативний) час встановлення або утримання, але не обидва одночасно.

На-жаль, не завжди можна виконати критерій установки і утримання, оскільки тригер може приймати на вхід сигнали реального часу, які можуть змінитися у будь-який момент, і які не є під контролем розробника. В такому випадку, найкраще, що може зробити розробник це зменшити імовірність помилки до певного рівня, в залежності від вимог щодо надійності даного кола. Одним із способів зменшення метастабільності, є підключення двох або більшої кількості тригерів послідовно у ланцюг, так що вихід кожного з них подається на вхід наступного, а всі пристрої мають спільний синхроімпульс. За допомогою цього методу, імовірність може зменшуватися до дуже малого значення, але не до нуля. Імовірність виникнення метастабільності стає ближчою до нуля, якщо кількість тригерів у ланцюзі збільшується.

Див. також

Примітки

- http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER RS-триггер.

- http://it.fitib.altstu.ru/neud/shemotechnika/index.php?doc=teor&st=124 Схемотехника. ТЕМА 11. Триггерные схемы. Бистабильна ячейка. Схема устранения дребезга контактов. Асинхронные и синхронные триггеры. Однотактные и двухтактные триггеры. 11.1. Асинхронные RS-триггеры. 11.1.1. RS — триггер на двух элементах «2И-НЕ».

- http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER D-триггер.

- http://dfe3300.karelia.ru/koi/posob/log_basis/triger1.htmlЛогические основы ЭВМ. D-Триггер Архівовано 1 лютого 2009 у Wayback Machine.

- http://cxem.net/beginner/beginner15.php Триггеры. Тактируемый D-триггер

- http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#TTRIGGER Т-триггер

- http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER JK-триггер

- http://dfe3300.karelia.ru/koi/posob/log_basis/triger3.html Архівовано 4 червня 2009 у Wayback Machine. Логические основы ЭВМ. JK-триггер

- www.gelezo.com — Триггеры

- Harris, S; Harris, D (2016). Digital Design and Computer Architecture - ARM Edition,. Morgan Kaufmann, Waltham, MA. ISBN 978-0-12-800056-4.

- Chaney, Thomas J.; Molnar, Charles E. (April 1973). Anomalous Behavior of Synchronizer and Arbiter Circuits. IEEE Transactions on Computers C–22 (4): 421–422. ISSN 0018-9340. doi:10.1109/T-C.1973.223730.