Перегони сигналів

Перегони сигналів — явище невідповідності роботи реальних цифрових пристроїв та змодельованих схем. Це відбувається через перехідні процеси та затримки у реальних схемах — сигнал не приходить, не наростає та не спадає миттєво. Таким чином, якщо сигнал вийшов із якогось джерела у час t0 ,а проміжне коло, наприклад логічний елемент, вносить затримку tз , то сигнал затримається на час tз , а не з'явиться на виході логічного елемента миттєво.

Приклад

Коректність роботи пристроїв залежить від електричних параметрів компонентів, розглянемо приклад некоректної роботи.

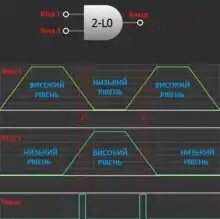

Нехай існує деякий логічний елемент логічний елемент AND. Подаємо на нього послідовно 3 пари сигналів 10,01,10 , де 1 — високий рівень, 0 — низький рівень.

За таких умов на виході ідеальної схеми AND завжди повинен бути низький рівень.

Оскільки сигнал має час наростання/спадання та може випереджати/відставати від іншого сигналу то отримаємо наступні процеси:

- На вході 1 — високий рівень («1»), на вході 2 низький рівень («0»). На виході низький рівень («0»).

- На вході 1 — спадаючий сигнал, на вході 2 — наростаючий сигнал. На виході невизначений сигнал, коли наростання одного сигналу «зустрінеться» зі спаданням іншого сигналу у точці, де напруга буде достатньою для високого рівня ми отримаємо небажаний імпульс на виході.

- На вході 1 — «0», на вході 2 — «0». На виході «0».

- На вході 2 — спадаючий сигнал, на вході 1 — наростаючий сигнал. На виході невизначений сигнал, коли наростання одного сигналу «зустрінеться» зі спаданням іншого сигналу у точці, де напруга буде достатньою для високого рівня ми отримаємо небажаний імпульс на виході.

- На вході 1 — «1», на вході 2 «0». На виході «0».

Усунення

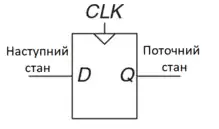

Для усунення ефекту перегонів сигналів використовують регістри, котрі реагують не на рівень, а на фронт тактового імпульсу і тоді говорять, що стан синхронізований із тактовою частотою. Наприклад D-Flip-Flop

Джерела

- Digital Design and Computer Architecture р.2.6.1

- Digital Design and Computer Architecture р.3.3.2