I²C

I2C — послідовна шина даних для зв'язку інтегральних схем, розроблена фірмою Philips на початку 1980-х як проста шина внутрішнього зв'язку для створення керуючої електроніки. Використовується для з'єднання низькошвидкісних периферійних компонентів з материнською платою, вбудовуваними системами та мобільними телефонами. Назва є абревіатурою слів Inter-Integrated Circuit. 1 жовтня 2006 року скасовані ліцензійні відрахування за використання протоколу I2C. Однак, відрахування зберігаються для виділення ексклюзивної підлеглої адреси на шині I2C.

Історія та схемотехніка

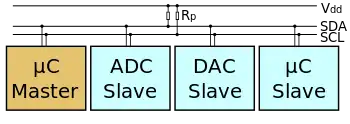

I2C використовує дві двонапрямлених лінії, підтягнуті до напруги живлення та керовані через відкритий колектор або відкритий стік — послідовна лінія даних (SDA, англ. Serial DAta) і послідовна лінія тактування (SCL, англ. Serial CLock). Стандартні напруги +5 В або +3,3 В, проте допускаються й інші.

Класична адресація включає 7-бітовий адресний простір з 16 зарезервованими адресами. Це означає до 112 вільних адрес для підключення периферії на одну шину.

Основний режим роботи — 100 кбіт/с; 10 кбіт/с в режимі роботи із зниженою швидкістю. Зауважимо, що стандарт допускає припинення тактування для роботи з повільними пристроями.

Після перегляду стандарту 1992 року стає можливим підключення ще більшої кількості пристроїв на одну шину (за рахунок можливості 10-бітної адресації), а також велику швидкість до 400 кбіт/с у швидкісному режимі. Відповідно, доступна кількість вільних вузлів зросла до 1008. Максимальна допустима кількість мікросхем, приєднаних до однієї шині, обмежується максимальною ємністю шини в 400 пФ.

Версія стандарту 2.0, випущена 1998 року представила високошвидкісний режим роботи зі швидкістю до 3,4 Мбіт/с зі зниженим енергоспоживанням. Остання версія 2.1 2001 року включила лише незначні доопрацювання.

Принцип роботи

Стан СТАРТ і СТОП

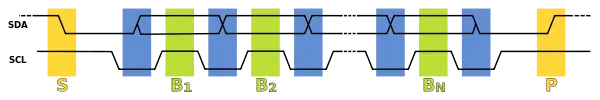

Процедура обміну починається з того, що ведучий (вузол, який ініціює передачу даних) формує стан СТАРТ: генерує перехід сигналу лінії SDA з ВИСОКОГО стану в низький при високому рівні на лінії SCL. Цей перехід сприймається усіма пристроями, підключеними до шини, як ознака початку процедури обміну. Генерація синхросигналу — це завжди обов'язок ведучого; кожний ведучий генерує свій власний сигнал синхронізації при пересиланні даних по шині. Процедура обміну завершується тим, що ведучий формує стан СТОП — перехід стану лінії SDA з низького стану в ВИСОКИЙ при високому стані лінії SCL. Стани СТАРТ і СТОП завжди виробляються ведучим. Вважається, що шина зайнята після фіксації стану СТАРТ. Шина вважається звільненою через деякий час після фіксації стану СТОП. При передачі посилок по шині I2C кожний ведучий генерує свій синхросигнал на лінії SCL. Після формування стану СТАРТ, ведучий опускає стан лінії SCL в НИЗЬКИЙ стан і виставляє на лінію SDA старший біт першого байта повідомлення. Кількість байт в повідомленні не обмежена. Специфікація шини I2C дозволяє зміни на лінії SDA лише при низькому рівні сигналу на лінії SCL. Дані дійсні та повинні залишатися стабільними лише під час ВИСОКОГО стану синхроімпульсу. Для підтвердження прийому байта від ведучого-передавача веденим-приймачем в специфікації протоколу обміну по шині I2C вводиться спеціальний біт підтвердження, який виставляється на шину SDA після прийому 8 біта даних.

Підтвердження

Таким чином передача 8 біт даних від передавача до приймача завершуються додатковим циклом (формуванням 9-го тактового імпульсу лінії SCL), при якому приймач виставляє низький рівень сигналу на лінії SDA, як ознаку успішного прийому байта.

Підтвердження при передачі даних обов'язкове, крім випадків закінчення передачі веденою стороною. Відповідний імпульс синхронізації генерується ведучим. Передавач відпускає (ВИСОКУ) лінію SDA на час синхроімпульсу підтвердження. Приймач повинен утримувати лінію SDA протягом ВИСОКОГО стану синхроімпульсу підтвердження в стабільному НИЗЬКОМУ стані.

У тому випадку, коли ведений-приймач не може підтвердити свою адресу (наприклад, коли він виконує в цей момент будь-які функції реального часу), лінія даних повинна бути залишена в ВИСОКОМУ стані. Після цього ведучий може видати сигнал СТОП для переривання пересилання даних. Якщо у пересиланні бере участь ведучий-приймач, то він повинен повідомити про закінчення передачі веденого-передавача шляхом непідтвердження останнього байта. Ведений-передавач повинен звільнити лінію даних для того, щоб дозволити ведучому видати сигнал СТОП або повторити сигнал СТАРТ.

Синхронізація

Синхронізація виконується з використанням підключення до лінії SCL за правилом монтажного І. Це означає, що ведучий не має монопольного права на керування переходом лінії SCL з НИЗЬКОГО стану в ВИСОКИЙ. У тому випадку, коли веденому потрібен додатковий час на обробку прийнятого біта, він має можливість утримувати лінію SCL в низькому стані до моменту готовності до прийому наступного біта. Таким чином, лінія SCL буде знаходитися в НИЗЬКОМУ стані протягом найдовшого НИЗЬКОГО періоду синхросигналів.

Пристрої з більш коротким найнижчими періодом будуть входити в стан очікування на час, поки не скінчиться довгий період. Коли у всіх задіяних пристроїв скінчиться НИЗЬКИЙ період синхросигналу, лінія SCL перейде в ВИСОКИЙ стан. Всі пристрої почнуть проходити ВИСОКИЙ період своїх синхросигналів. Перший пристрій, у якого скінчиться цей період, знову встановить лінію SCL в НИЗЬКИЙ стан. Таким чином, НИЗЬКИЙ період синхролініі SCL визначається найдовшим періодом синхронізації з усіх задіяних пристроїв, а ВИСОКИЙ період визначається самим коротким періодом синхронізації пристроїв.

Механізм синхронізації може бути використаний приймачами як засіб керування пересиланням даних на байтовому та бітовому рівнях.

На рівні байта, якщо пристрій може приймати байти даних з великою швидкістю, але вимагає певний час для збереження прийнятого байта або підготовки до прийому наступного, то воно може утримувати лінію SCL в НИЗЬКОМУ стані після прийому та підтвердження байта, переводячи таким чином передавач в стан очікування.

На рівні бітів, пристрій, такий як мікроконтролер без вбудованих апаратних схем I2C або з обмеженими схемами, може уповільнити частоту синхроімпульсів шляхом продовження їх НИЗЬКОГО періоду. Таким чином швидкість передачі будь-якого ведучого адаптується до швидкості повільного пристрою.

Адресація в шині I2C

Кожен пристрій, підключений до шини, може бути програмно адресований за унікальною адресою. Для вибору приймача повідомлення передавач використовує унікальну адресну компоненту у форматі посилки. При використанні однотипних пристроїв, ІС часто мають додатковий селектор адреси, який може бути реалізований як у вигляді додаткових цифрових входів селектора адреси, так і у вигляді аналогового входу. При цьому адреси таких однотипних пристроїв виявляються рознесені в адресному просторі пристроїв, підключених до шини.

У звичайному режимі використовується 7-бітна адресація.

Процедура адресації на шині I2C полягає в тому, що перший байт після сигналу СТАРТ визначає, який ведений адресується передавачем для проведення циклу обміну. Виняток становить адреса «Загального виклику», який адресує всі пристрої на шині. Коли використовується ця адреса, всі пристрої в теорії повинні послати сигнал підтвердження. Однак, пристрої, які можуть обробляти «загальний виклик», на практиці трапляються рідко.

Перші сім бітів першого байта утворюють адресу веденого. Восьмий, молодший біт, визначає напрям пересилання даних. «Нуль» означає, що ведучий буде записувати інформацію до обраного веденого. «Одиниця» означає, що ведучий буде зчитувати інформацію з веденого.

Після того, як адреса послана, кожний пристрій в системі порівнює перші сім біт після сигналу СТАРТ зі своєю адресою. при збігу пристрій вважає себе обраним як ведений-приймач або як ведений-передавач, залежно від біта напряму.

Адреса веденого може складатися з фіксованої та програмованої частини. Часто трапляється, що в системі буде кілька однотипних пристроїв (Наприклад ІМС пам'яті, або драйверів світлодіодних індикаторів), тому за допомогою програмованої частини адреси стає можливим підключити до шини максимально можливу кількість таких пристроїв. Кількість програмованих біт в адресі залежить від кількості вільних виводів мікросхеми. Іноді використовується один вивід з аналоговою установкою програмованого діапазону адрес. При цьому залежно від потенціалу на цьому адресному виведенні ІМС, можливе зміщення адресного простору драйвера так, щоб однотипні ІМС не конфліктували між собою на загальній шині.

Всі спеціалізовані ІМС, що підтримують роботу в стандарті шини I2C, мають набір фіксованих адрес, перелік яких зазначений виробником в описах контролерів.

Комбінація біт 11110ХХ адреси зарезервована для 10-бітної адресації.

Як випливає з специфікації шини, допускаються як прості формати обміну, так і комбіновані, коли в проміжку від стану СТАРТ до стану СТОП ведучий та ведений можуть виступати і як приймач, і як передавач даних. Комбіновані формати можуть бути використані, наприклад, для керування послідовною пам'яттю.

Під час першого байта даних можна передавати адресу в пам'яті, який записується у внутрішній регістр-засувку. Після повторення сигналу старту та адреси веденого видаються дані з пам'яті. Всі рішення про авто-Інкремент або декремент адреси, до якого стався попередній доступ, приймаються конструктором конкретного пристрою. Тому, в будь-якому випадку найкращий спосіб уникнути неконтрольованої ситуації на шині перед використанням нової (або раніше не використовуваної) ІМС слід ретельно вивчити її опис (datasheet або reference manual), отримавши його з сайту виробника. Більше того, виробники часто розміщують поруч більш докладні інструкції по застосуванню.

В будь-якому випадку, за специфікацією шини, всі пристрої, що розробляються, при отриманні сигналу СТАРТ або повторний СТАРТ повинні скинути логіку шини та підготуватися до прийому адреси.

Проте основні проблеми з використанням I2C шини виникають саме через те, що розробники «початківці», працюючи з I2C шиною, не враховують того факту, що ведучий (часто — мікропроцесор) не має монопольного права ні на одну з ліній шини.

Застосування

I2C знаходить застосування в пристроях, які передбачають простоту розробки та низьку собівартість виготовлення при відносно непоганий швидкості роботи.

Список можливих застосувань:

- доступ до модулів пам'яті NVRAM;

- доступ до низькошвидкісних ЦАП/АЦП;

- регулювання контрастності, насиченості та колірного балансу моніторів;

- регулювання звуку в динаміках;

- керування світлодіодами, в тому числі в мобільних телефонах;

- читання інформації з датчиків моніторингу та діагностики устаткування, наприклад, термостат центрального процесора або швидкість обертання вентилятора охолодження;

- читання інформації з годинника реального часу (кварцових генераторів);

- керування включенням/виключенням живлення системних компонент;

- інформаційний обмін між мікроконтролерами;

На дешевих пристроях часто I2C емулюється програмно з використанням технології Bit-banging.

Переваги

- необхідний всього один мікроконтролер для керування набором пристроїв;

- використовується всього дві лінії введення-виведення загального призначення;

- стандарт передбачає «гаряче» підключення та відключення пристроїв в процесі роботи системи

- вбудований в мікросхеми фільтр придушує сплески, забезпечуючи цілісність даних.

Переваги для конструкторів

- оскільки такі мікросхеми підключаються безпосередньо до шини без будь-яких додаткових ланцюгів, з'являється можливість модифікації та модернізації системи прототипу шляхом підключення та відключення пристроїв від шини.

- блоки на функціональній схемі відповідають мікросхемам, перехід від функціональної схеми до принципової відбувається швидко.

- немає потреби розробляти шинні інтерфейси, оскільки шина вже інтегрована в мікросхеми.

- інтегровані адресація пристроїв та протокол передачі даних дозволяють системі бути повністю програмно обумовленою.

- одні й ті ж типи мікросхем можуть бути часто використані в різних додатках.

- час розробки знижується, оскільки конструктори швидко знайомляться з часто використовуваними функціональними блоками та відповідними мікросхемами.

- мікросхеми можуть бути додані або прибрані з системи без надання впливу на інші мікросхеми, підключені до шини (якщо їх робота незалежна).

- проста діагностика збоїв та налагодження; порушення в роботі можуть бути негайно відслідковані.

- час розробки програмного забезпечення може бути знижене за рахунок використання бібліотеки повторно використовуваних програмних модулів.

Приклад системи з шиною I2C

У телевізорі:

- Мікроконтролер

- ФАПЧ синтезатор

- Флеш-пам'ять

- Мультисистемний декодер сигналів кольоровості

- Стереодекодер звуку

- Покращувач сигналу картинки

- HI-FI аудіопроцесор

- Відеопроцесор

- Одночіповий текст

- ІМС сигналів OSD

У базовій станції радіотелефону стандарту DECT

Підтримка операційними системами

- У Linux підтримка I2C забезпечується спеціальним модулем для кожного пристрою, сумісного з цим стандартом. Файл заголовків для написання клієнта I2C — /usr/include/linux/i2c.h. В OpenBSD також додана підтримка основних мікроконтролерів та сенсорів I2C;

- В Sinclair QDOS і Minerva QL підтримка здійснюється через набір розширень фірми TF Services;

- В AmigaOS доступ до пристроїв I2C здійснюється за допомогою бібліотеки i2c.library, написаної Вільгельмом Нойкером;

- eCos підтримує I2C для декількох архітектур.

- Материнські плати EPIA-M підтримують I2C на рівні форм-фактор Mini-ITX.

Похідні технології

I2C є основою ACCESS.bus, дисплейного інтерфейсного каналу даних (DDC) VESA, шини керування системними функціями SMBus, шини інтелектуального керування системою IPMB (варіант протоколу IPMI). У цих технологіях можливе використання різних напруг, частоти тактування та наявності ліній переривань.

TWI (Two Wire Interface) або TWSI (Two Wire Serial Interface) власне та ж сама шина I2C, але використовує іншу назву за ліцензійними причин. (Патенти на I2C вже скасовані)

Примітки

Див. також

Посилання

- Опис шини I2C RUS

- Шина I2C і як її використовувати (включаючи специфікацію) RUS

- Специфікації Philips I2C Архівовано 12 лютого 2007 у Wayback Machine.

- I2C(англ.)

- Introduction to I2C

- I2C Bus/Access Bus

- Using the I2C Bus with Linux

- OpenBSD iic(4) manual page[недоступне посилання з жовтня 2019]

- GNU/Linux package lm-sensors supports I2C bus, among others.

- massmind I2C page Source code, samples and technical information for using I2C with PC, PIC and SX microcontrollers.

- I2C bus

- Serial buses information page

- I2C Bus Technical Overview and Frequently Asked Questions

- The I2C Faq Version 2.0

- The Bus Buffer Resource. For 2-wire buses such as I2C, SMBus, PMBus, IPMB & IPMI

- I2C Licensing Information

- Інтерфейс I2C