Intel Core (мікроархітектура)

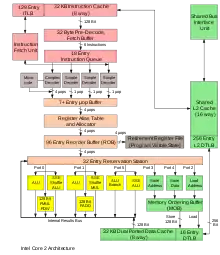

Мікроархітекту́ра Intel Core 2 є багатоядерною мікропроцесорною архітектурою, представленою фірмою Intel в 1-му кварталі 2006 року. Мікроархітектура Intel Core заснована на оновленій версії ядра Yonah і може розглядатися як остання ітерація мікроархітектури Intel P6, яка веде свою історію з Pentium Pro, представленого в 1995 році. Надмірно високе енергоспоживання і завищені вимоги до охолодження процесорів, заснованих на мікроархітектурі NetBurst, і, в результаті, нездатність ефективно збільшувати тактову частоту, а також інші вузькі місця, такі, як неефективність конвеєра, є головними причинами, чому Intel відмовилася від мікроархітектури NetBurst. Мікроархітектура Intel Core 2 була розроблена командою Intel Israel (IDC), яка раніше розробила мобільний процесор Pentium M.

Мікроархітектура Intel Core 2 забезпечує високу продуктивність, енергозбереження та швидкодію в багатозадачних середовищах. Вона має кілька ядер і апаратну підтримку віртуалізації (Intel VT), а також x64 і SSSE3.

Перші процесори, що використали цю архітектуру, вийшли під кодовими назвами Merom, Conroe і Woodcrest. Merom призначався для мобільних комп'ютерів, Conroe — для настільних систем, а Woodcrest — для серверів і робочих станцій. Хоча їх архітектури ідентичні, ці три лінії процесорів відрізняються використовуваним роз'ємом, типом шини і споживанням енергії. Частина заснованих на мікроархітектурі Core процесорів має марку Pentium Dual-Core, а процесори нижчого цінового сегмента — марку Celeron. Процесори для серверів і робочих станцій продаються під маркою Xeon, а для користувачів настільних і мобільних ПК — як Core 2. Незважаючи на свою назву, процесори, продавані як Intel Core, фактично не використовують мікроархітектуру Core 2.

Wide Dynamic Execution

Мікроархітектура Intel Core 2 проектована з нуля, але з ідеями мікроархітектури Pentium M. Довжина виконавчого конвеєра становить 14 ступенів — менше половини від довжини конвеєра в попередньому поколінні Prescott (31 ступінь), і є ключовою особливістю технології Динамічного виконання команд.

Кожне ядро мікропроцесора може отримувати, обробляти, виконувати і відкидати до чотирьох повних команд одночасно. Це значно підвищує продуктивність у порівнянні з конкуруючими процесорними технологіями P6, Pentium M (Banias, Dothan, Yonah) і NetBurst), що підтримують одночасну обробку тільки трьох команд.

Advanced Smart Cache

Нова архітектура оптимізована під двоядерну архітектуру процесора. Основний кеш першого рівня L1 пов'язаний із загальною для обох ядер динамічно розподіленою кеш-пам'яттю другого рівня L2 (дані, що містяться в L1, обов'язково містяться і в L2) для досягнення максимальної продуктивності на ват споживаної потужності і поліпшення масштабованості.

Macro Fusion

Ще однією новою технологією, включеною в мікроархітектуру Intel Core 2 при проектуванні, є Технологія макро-злиття (Macro Fusion), яка дозволяє об'єднувати деякі поширені інструкції x86 в одну команду для виконання. У попередніх версіях процесорної мікроархітектури кожна інструкція декодувати незалежно від інших. При використанні Macro Fusion деякі пари інструкцій (наприклад, інструкція порівняння і умовного переходу) при декодуванні можуть об'єднуватися в одну мікроінструкцію (micro-op), яка в подальшому буде виконуватися саме як одна мікроінструкція. Для ефективної підтримки цієї технології в архітектурі Intel Core 2 використовуються розширені блоки АЛП, які здатні підтримати виконання таких злитих мікроінструкцій.