JTAG

JTAG (скорочення від англ. Joint Test Action Group; вимовляється «джей-тáг») — назва робочої групи з розробки стандарту IEEE 1149. Пізніше це скорочення стало міцно асоціюватися з розробленим цією групою спеціалізованим апаратним інтерфейсом на базі стандарту IEEE 1149.1. Офіційна назва стандарту Standard Test Access Port and Boundary-Scan Architecture. Послідовний інтерфейс призначений для підключення складних цифрових мікросхем чи пристроїв рівня друкованої плати до стандартної апаратури тестування і налагодження.

На поточний момент інтерфейс став промисловим стандартом. Практично всі скільки-небудь складні цифрові мікросхеми оснащено цим інтерфейсом для:

- вихідного контролю мікросхем при виробництві;

- тестування зібраних друкованих плат;

- прошивки мікросхем з пам'яттю;

- налагоджувальних робіт при проектуванні апаратури і програмного забезпечення.

Метод тестування, реалізований в стандарті, отримав назву Boundary Scan (граничне сканування). Назва відображає первісну ідею процесу: в мікросхемі виділяються функціональні блоки, входи яких можна від'єднати від решти схеми, подати задані комбінації сигналів і оцінити стан виходів кожного блоку. Весь процес проводиться спеціальними командами по інтерфейсу JTAG, при цьому ніякого фізичного втручання не потрібно. Розроблено стандартну мову керування даним процесом — Boundary Scan Description Language (BSDL).

Порт тестування

Порт тестування (англ. TAP — Test Access Port) являє собою чотири або п'ять виділених виводів мікросхеми: ТСК, TMS, TDI, TDO і (опціонально) TRST.

- TDI (test data input — «вхід тестових даних») — вхід послідовних даних периферійного сканування. Команди і дані вводяться в мікросхему з цього виводу по передньому фронту сигналу TCK;

- TDO (test data output — «вихід тестових даних») — вихід послідовних даних. Команди і дані виводяться з мікросхеми з цього виводу по задньому фронту сигналу TCK;

- TCK (test clock — «тестове тактування») — тактує роботу вбудованого автомата управління периферійним скануванням. Максимальна частота сканування периферійних осередків залежить від використовуваної апаратної частини і на даний момент обмежена 25 … 40 МГц ;

- TMS (test mode select — «вибір режиму тестування») — забезпечує перехід схеми в / з режиму тестування і перемикання між різними режимами тестування.

- TRST (test reset — «скидання інтерфейсу тестування») — необов'язковий сигнал, який скидає інтерфейс тестування у початковий стан.

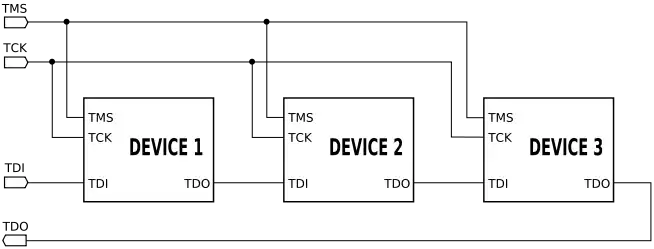

Стандарт передбачає можливість підключення великої кількості пристроїв (мікросхем) через один фізичний порт (з'єднувач). Це можливо завдяки послідовному ввімкненню пристроїв та роботі з ними по заданому номеру у ланцюжку.

У деяких випадках до перерахованих сигналів додається сигнал TRST для ініціалізації порту тестування, що необов'язково, оскільки ініціалізація можлива шляхом подачі певної послідовності сигналів на вхід TMS.

Робота засобів забезпечення інтерфейсу JTAG підкоряється сигналам автомата управління, вбудованого в мікросхему. Стан автомата визначаються сигналами TDI і TMS порту тестування. Певне поєднання сигналів TMS і TCK забезпечує введення команди для автомата і її виконання.

Якщо на платі встановлено кілька пристроїв, що підтримують JTAG, вони можуть бути об'єднані в загальну послідовність. Унікальною особливістю JTAG є можливість програмування не тільки самого мікроконтролера (або ПЛІС), але і підключеної до його виводів мікросхеми флеш-пам'яті. Причому існує два способи програмування флеш-пам'яті з використанням JTAG: через завантажувач з подальшим обміном даними через пам'ять процесора, або через пряме управління виводами мікросхеми.

Див. також

Посилання

- IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture(англ.) Офіційний IEEE 1149.7 Стандарт.

- JTAG 101 - IEEE 1149.x and Software Debug (англ.).

- IEEE Std 1149.1 (JTAG) Testability Primer (англ.)

- JTAG Tutorial and Boundary-Scan Applications (англ.)