Периферійне сканування

Перифері́йне сканува́ння (англ. boundary scan) — вид структурного тестування друкованої плати з встановленими на неї компонентами, заснований на застосуванні в деяких мікросхемах стандарту IEEE 1149.1. Широко використовується також термін «Граничне сканування». Результатом периферійного сканування є інформація про наявність в електричних колах типових несправностей, що виникають при виробництві друкованих плат:

- коротких замикань (bridges),

- непропайок (opens),

- залипань на 0 або 1 (stuck at 0, stuck at 1),

- обривів доріжок.

Периферійним сканування було названо через те, що відповідні мікросхеми можуть за певних умов самі протестувати своє оточення - периферію - на наявність несправностей.

Периферійне сканування було запропоновано вперше ще в 1985 році і було реалізовано в 1990 році у вигляді стандарту IEEE 1149.1. Протягом перших декількох років існування периферійне сканування поступово набрало популярність, так як виробники мікросхем пропонували все більшу кількість компонентів, що підтримують стандарт IEEE 1149.1.

Відповідність стандарту IEEE 1149.1

Для того, щоб відповідати стандарту, мікросхема повинна містити: JTAG-порт мікросхеми і осередки периферійного сканування

- 4-х або 5-ти проводний порт тестового доступу (TAP - Test Access Port), що складається з наступних ліній:

- TDI (Test Data Input) - вхід тестової послідовності,

- TDO (Test Data Output) - вихід тестової послідовності,

- TMS (Test Mode Select) - вибір тестового режиму,

- TCK (Test Clock) - синхронізація,

- TRST (Test Reset) - опціональна лінія скидання.

- внутрішні осередки периферійного сканування (BS Cells)

- регістри периферійного сканування (BS Registers)

- додаткову перемикаючу обв'язку (TAP Controller)

Крім того, виробник мікросхеми повинен надати так званий BSDL-файл (англ. Boundary Scan Description Language), який повністю описує логіку периферійного сканування даного типу мікросхем.

Застосування периферійного сканування

Для застосування периферійного сканування необхідна наявність в тестованому пристрої компонентів, які його підтримують. Іноді їх називають компонентами з JTAG-інтерфейсом. Безліч мікросхем неабиякого числа виробників вже підтримують стандарт IEEE 1149.1.

Щоб отримати гарне тестове покриття немає необхідності в тому, щоб всі компоненти на платі мали JTAG-інтерфейс. Наприклад, багато блоків, що складаються з несканованих компонентів, т. зв. кластерів, можуть тестуватися, незважаючи на відсутність прямого доступу для сканування. У деяких випадках контроль і детальне тестування всієї плати (включаючи пам'ять) здійснюються за допомогою одного або двох компонентів, що підтримують периферійне сканування.

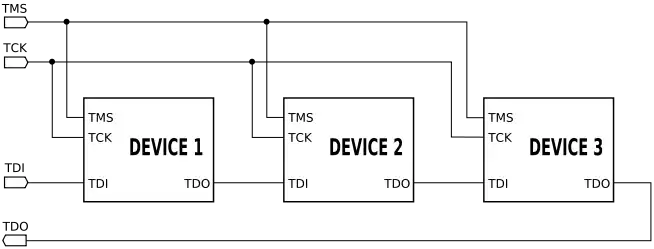

Мікросхеми, що підтримують периферійне сканування, з'єднуються в один або кілька окремих ланцюжків. При цьому вивід TDO однієї мікросхеми з'єднується з виводом TDI іншої. До всіх мікросхем підводяться сигнали TCK і TMS для контролю всієї «тестової інфраструктури».

Механізм периферійного сканування

Потім якась тестова послідовність (тестовий вектор - Test Vector), двійкова - складається з нулів і одиниць, вводиться в тестовий порт (TAP). Вона проходить послідовно через всі комірки периферійного сканування (BS Cells). На виході (TDO) вона аналізується спеціальним програмним забезпеченням, після чого робляться відповідні висновки про стан інфраструктури даної мікросхеми.

Якщо тестова послідовність прийшла в незміненому стані - то робиться висновок про відсутність коротких замикань і непропайок у мікросхеми. Якщо послідовність змінилася - то навпаки.

Насправді, це не зовсім так. Конфігурації сучасних цифрових пристроїв настільки складні, що по одному тестовому вектору зазвичай неможливо судити про всю інфраструктуру. Внаслідок чого використовуються одночасно кілька тестових векторів. У завдання ж відповідного програмного забезпечення входить визначення виду і мінімальної (ненадлишкової) кількості цих тестових векторів.

Види тестів та програм, які можуть бути реалізовані за допомогою периферійного сканування

- Тест інфраструктури: перевірка цілісності кіл JTAG-інтерфейсу і коректної установки мікросхем, що підтримують периферійне сканування.

- Тест міжз'єднань: перевірка кіл, пов'язаних з компонентами, що підтримують периферійне сканування. Сюди включаються з'єднання між цими компонентами, їх не підключені виводи і кола, що виходять на зовнішні роз'єми. У тест міжз'єднань можуть бути включені транспарентні пристрої, такі як: буфери, резистори, інша єднальна логіка. Часто даний етап включає перевірку резисторів підтяжки.

- Тест пам'яті: тестування міжз'єднань з пристроями пам'яті. Дозволяє визначити дефекти на шинах адреси і даних і на контрольних колах таких пристроїв як SRAM, DRAM, SDRAM, DDR, DDR2, FIFO, а також різних флеш-ПЗУ. По суті це тестування з'єднань з пам'яттю.

- Тест кластерів: перевірка кіл, пов'язаних з будь-якими пристроями, які не підтримують периферійне сканування. При наявності моделі функціонування того або іншого пристрою можлива автоматична генерація тестових векторів і для них. Типові «кластери» при тестуванні методом периферійного сканування - це різна логіка (для автоматичної генерації тестів використовується таблиця істинності), інтерфейсні мікросхеми (наприклад RS-232, Ethernet і т. д.), пристрої відображення інформації.

- Програмування флеш-ПЗУ: використовується той же механізм, що і при тестуванні кластерів.

- Програмування або конфігурація ПЛІС: використовується JTAG-інтерфейс.