PCI Express

PCI Express або PCIe або PCI-E, (також відома як 3GIO for 3rd Generation I/O; не плутати з PCI-X або PXI) — комп'ютерна шина, що використовує програмну модель шини PCI і високопродуктивний фізичний протокол, заснований на послідовній передачі даних.[1]

Започаткована у липні 2002 року компанією Intel.

Історія розробки

Розвитком стандарту PCI Express займається організація PCI Special Interest Group (PCI-SIG).

На відміну від шини PCI, що використала для передачі даних спільну шину, PCI Express, в загальному випадку, є пакетною мережею з топологією типу зірка, пристрої PCI Express взаємодіють між собою через середовище, утворене комутаторами, при цьому кожен пристрій безпосередньо зв'язаний з'єднанням типу точка-точка з комутатором.

Крім того, шиною PCI Express підтримується:

- гаряча заміна карт;

- гарантована смуга пропускання (QoS);

- управління енергоспоживанням;

- контроль цілісності передаваних даних.

Розробку стандарту PCI Express почала фірма AMD після відмови від шини InfiniBand. Офіційно перша базова специфікація PCI Express з'явилася в липні 2002 року[1].

Шина PCI Express націлена на використання тільки як локальна шина. Оскільки програмна модель PCI Express багато в чому успадкована від PCI, то існуючі системи і контролери можуть бути допрацьовані для використання шини PCI Express заміною тільки фізичного рівня, без доопрацювання програмного забезпечення. Висока пікова продуктивність шини PCI Express дозволяє використовувати її замість шин AGP і тим більше PCI і PCI-X, що призвело до заміни цих шин на PCI Express в персональних комп'ютерах.

Опис протоколу

Для підключення пристрою PCI Express використовується двонаправлене послідовне з'єднання типу точка-точка, зване lane; це дуже відрізняється від PCI, в якій всі пристрої підключаються до спільної 32-розрядної паралельної однонаправленої шини.

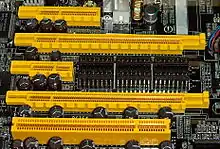

З'єднання між двома пристроями PCI Express називається link, і складається з одного (званого 1x) або декількох (2x, 4x, 8x, 12x, 16x і 32x) двонаправлених послідовних з'єднань lane. Кожен пристрій повинен підтримувати з'єднання 1x.

На електричному рівні кожне з'єднання використовує низьковольтну диференціальну передачу сигналу (LVDS)[1], прийом і передача інформації проводиться кожним пристроєм PCI Express по окремих двох провідниках, таким чином, у простому випадку, пристрій підключається до комутатора PCI Express всього чотирма провідниками.

Використання подібного підходу має такі переваги:

- карта PCI Express поміщається і коректно працює в будь-якому слоті тої або ж більшої пропускній спроможності (наприклад, карта x1 працюватиме в слотах x4 і x16);

- слот більшого фізичного розміру може використовувати не всі lane (наприклад, до слоту 16x можна підвести лінії передачі інформації, відповідні 1x або 8x, і все це нормально функціонуватиме; проте, при цьому необхідно підключити всі лінії «живлення» і «земля», необхідні для слота 16x).

В обох випадках, на шині PCI Express використовуватиме максимальну кількість lane'ів доступних як для карти, так і для слоту. Проте це не дозволяє пристрою працювати в слоті, призначеному для карт з меншою пропускною спроможністю шини PCI Express (наприклад, карта x4 фізично не поміститься в слот x1, не зважаючи на те, що вона могла б працювати в слоті x1 з використанням тільки одного lane).

PCI Express пересилає всю керувальну інформацію, включно з перериваннями, через ті ж лінії, що використовуються для передавання даних. Послідовний протокол ніколи не може бути заблокований, таким чином затримки шини PCI Express цілком порівнянні з такими для шини PCI (відмітимо, що шина PCI для передавання сигналу про запит на переривання використовує окремі фізичні лінії IRQ#A, IRQ#B, IRQ#C, IRQ#D).

У всіх високошвидкісних послідовних протоколах (наприклад, Gigabit Ethernet), інформація про синхронізацію повинна бути вбудована в передаваний сигнал. На фізичному рівні, PCI Express використовує загальноприйнятий метод кодування 8B/10B (8 бітів даних замінюються на 10 бітів, передаваних по каналу, таким чином 20 % передаваного по каналу трафіку є надмірними), що дозволяє підвищити стійкість до перешкод.

Деякі протоколи (наприклад, SONET/SDH) використовують інший метод перешкодозахисного кодування, який називається скремблінг (англ. scrambling) для вбудовування інформації про синхронізацію в потік даних. Специфікація PCI Express також передбачає алгоритм скремблінгу, але скремблінг PCI Express відрізняється від такого в SONET.

Пропускна здатність

Пропускна здатність з'єднання lane становить 2,5 Гбіт/с.[1] Для розрахунку пропускної спроможності з'єднання шини (link) необхідно врахувати те, що в кожному з'єднанні передача дуплексна, а також врахувати застосування кодування 8B/10B (8 бітів в 10). Наприклад, дуплексна пропускна спроможність з'єднання 1x (P1x) становить:

- ГБ/сек

де

- 2,5 — пропускна спроможність одного lane, Гбіт/с;

- 2 — врахування того, що з'єднання 1x складається з двох lane;

- 0,8 — коефіцієнт, що враховує використання коду 8B/10B;

- 8 — коефіцієнт перерахунку Гбіт/с в ГБ/с.

Пропускна спроможність, з урахуванням двонаправленої передачі, для шин PCI Express з різною кількістю зв'язків вказана в таблиці:

| Версія інтерфейсу | 1x | 2x | 4x | 8x | 12x | 16x | 32x |

|---|---|---|---|---|---|---|---|

| Пропускна здатність PCI Express 1.0, ГБ/c | 0,5 | 1 | 2 | 4 | 6 | 8 | 16 |

| Пропускна здатність PCI Express 2.0, ГБ/c | 1 | 2 | 4 | 8 | 12 | 16 | 32 |

| Пропускна здатність PCI Express 3.0, ГБ/c | 2 | 4 | 8 | 16 | 24 | 32 | 64 |

| PCIe 4.0[2] | 4 | 8 | 16 | 32 | 48 | 64 | 128 |

| PCIe 5.0[3][4][5] | 8 | 16 | 32 | 64 | 96 | 128 | 256 |

| PCIe 6.0[6] | 16 | 32 | 64 | 128 | 192 | 256 | 512 |

PCI Express 2.0

Група PCI-SIG випустила специфікацію PCI Express 2.0[1] 15 січня 2007 року.

Основні нововведення в PCI Express 2.0:

- Збільшена пропускна здатність — специфікація PCI Express 2.0 визначає максимальну пропускну здатність одного з'єднання lane як 5 Гбіт/с[1], при цьому збережена сумісність з PCI Express 1.1 таким чином, що плата розширення, що підтримує стандарт PCIE 1.1 може працювати, будучи встановленою в слот PCIe 2.0. Внесені вдосконалення в протокол передачі між пристроями і програмну модель.

- Динамічне управління швидкістю — для управління швидкістю роботи зв'язку.

- Сповіщення про пропускну здатність — для сповіщення ПЗ (операційної системи, драйверів пристроїв тощо) про зміни швидкості і ширину шини.

- Розширення структури можливостей — розширення керувальних регістрів для кращого управління пристроями, слотами і інтерконектом.

- Служби управління доступом — опціональні можливості управління транзакціями точка-точка.

- Управління таймаутом виконання

- Скидання[Куди?] на рівні функцій — опціональний механізм для скидання функцій (маються на увазі PCI funcs) усередині пристрою (PCI device).

- Перевизначення межі за потужністю — для перевизначення ліміту потужності слоту при приєднанні пристроїв, які споживають більшу потужність.

Зовнішня кабельна специфікація PCIe

7 лютого 2007 року PCI-SIG випустила специфікацію зовнішньої кабельної системи PCIe. Нова специфікація дозволяє використовувати кабелі завдовжки до 10 метрів, що працюють з пропускною спроможністю 2,5 Гбіт/с[1].

PCI Express 3.0

Затверджена у листопаді 2010 року, забезпечує пропускну здатність 8 Гбіт/с на одну лінію.

PCI Express 4.0

Специфікація опублікована у жовтні 2017 року й має пропускну здатність 16 Гбіт/с на одну лінію.

PCI Express 5.0

В травні 2019 року з'явилася фінальна версія стандарту PCI Express 5.0[5]. Швидкість передачі даних по шині PCI Express без врахування дуплексу становить 32 GT/s.[7]. Для 4-х ліній швидкість передачі даних становить 16 Гбайт/с, для 16-ти ліній — 64 Гбайт/с[5].

PCI Express 6.0

Фінальна специфікація стандарту PCI Express 6.0 планується до публікації в 2021 р. Очікувана швидкість передачі даних без врахування дуплексу - 32 Гбайт/с для 4-х ліній і 128 Гбайт/с для 16-ти ліній[6].

Форм-фактори

- Низькопрофільні карти

- Mini Card — заміна форм-фактора Mini PCI. На роз'єм Mini Card виведені шини: x1 PCIe, USB 2.0 і SMBus.

- ExpressCard — подібний до форм-фактора PCMCIA. На роз'єм Mini Card виведені шини x1 PCIe і USB 2.0, карти ExpressCard підтримують гаряче підключення.

- AdvancedTCA — форм-фактор для телекомунікаційного устаткування.

- Кабельні специфікації PCI Express дозволяють доводити довжину одного з'єднання до десятків, а то і сотень метрів, що робить можливим створення «розібраних» ЕОМ.

- Mobile PCI Express Module — промисловий форм-фактор, створений для ноутбуків фірмою NVIDIA.

Конкурентні протоколи

Окрім PCI Express існує ще ряд високошвидкісних стандартизованих послідовних інтерфейсів, ось деякі з них: HyperTransport, InfiniBand, RapidIO, StarFabric. Кожен інтерфейс має своїх прихильників серед промислових компаній, оскільки на розробку специфікацій протоколів вже пішли значні суми, і кожен консорціум прагне підкреслити переваги саме свого інтерфейсу.

Стандартизований високошвидкісний інтерфейс з одного боку повинен мати гнучкість і розширюваність, а з іншого боку має забезпечувати низький час затримки і невисокі накладні витрати (тобто частка службової інформації пакету не повинна бути велика). По суті, відмінності між інтерфейсами полягають саме у вибраному компромісі між цими двома суперечливими напрямами.

Наприклад, додаткова службова маршрутна інформація в пакеті дозволяє організувати складну і гнучку маршрутизацію пакету, але збільшує накладні витрати на обробку пакету, також знижується пропускна спроможність інтерфейсу, ускладнюється програмне забезпечення, яке ініціалізує і настроює пристрої, підключені до інтерфейсу. При необхідності забезпечення гарячого підключення пристроїв необхідне спеціальне програмне забезпечення, яке б відстежувало зміну топології мережі. Прикладами інтерфейсів, які пристосовані для цього є RapidIO, InfiniBand і StarFabric.

Водночас, укоротивши пакети можна зменшити затримку при передачі даних, що є важливою вимогою до інтерфейсу пам'яті. Але невеликий розмір пакетів приводить до того, що частка службових полів пакету збільшується, що знижує ефективну пропускну здатність інтерфейсу. Прикладом інтерфейсу такого типу є HyperTransport.

Положення PCI Express — PCI Express потрапляє десь посередині між описаними підходами, шина призначена для роботи як системне з'єднання (локальна шина), а не з'єднання процесор-пам'ять або у складній маршрутизованій мережі. Крім того, PCI Express від початку замислювалася як шина, логічно сумісна з шиною PCI, що також внесло свої обмеження.

Див. також

Примітки

- Слюсар В.И. PCI Express. Лицо стандарта.// Мир автоматизации. – 2006. - № 1. - C. 38 – 41.

- Maximum PC | PCIe 4.0 to Double the Speed of PCIe 3.0

- Review Zone | PCI-SIG (англ.). pcisig.com. Процитовано 9 червня 2017.

- PCIe 5.0 Arriving in 2019 With 4x More Bandwidth Than PCIe 3.0 / Joel Hruska, June 9, 2017(англ.)

- Андрей Шиллинг (30 травня 2019). PCI Express 5.0 - представлены финальные спецификации. «Hardwareluxx». Архів оригіналу за 28 червня 2019. Процитовано 28 червня 2019.

- Стандарт PCI Express 6.0 будет утверждён в 2021 году. Overclockers.ru. 19 червня 2019. Архів оригіналу за 19 червня 2019. Процитовано 28 червня 2019.

- Hot Chips 2017: We'll See PCIe 4.0 This Year, PCIe 5.0 In 2019. Tom's Hardware (англ.). 29 серпня 2017. Процитовано 18 січня 2018.

Посилання

- PCI Special Interest Group(англ.)

- PCI Express Specifications and White Papers(англ.)

- Creating a Third Generation I/O Interconnect (PDF)(англ.)(PDF)

- Intel Developer Network for PCI Express Architecture(англ.)

- PCI Express пункт прибытия 2014 год(рос.)

- Maximum PC | PCIe 4.0 to Double the Speed of PCIe 3.0

- Інтерфейс PCI-Express. Основні характеристики і зворотна сумісність