Блок генерації адреси

Блок генерації адреси (БГА), іноді також називають адресним блоком обчислення (АБО)[1] — це функціональний блок центрального процесора, який обчислює адреси, що використовуються процесором для доступу до основної пам'яті. При наявності окремих схем що розраховують адреси, які працюють паралельно з рештою процесора, кількість циклів процесора, необхідних для виконання машинних команд можна зменшити, в результаті чого істотно підвищити продуктивність.[2][3]

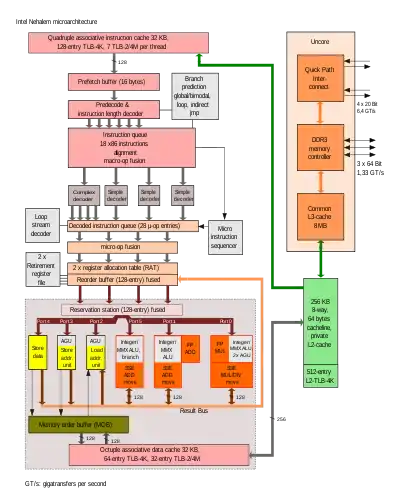

Можливості в БГА залежать від конкретного процесора і його архітектури. Таким чином, деякі БГА реалізують та надають більше операцій з обчислення адрес, в той час як інші мають більш просунуті спеціалізовані інструкції, що можуть працювати одночасно з кількома операндами[2][3]. Крім того, деякі процесорні архітектури містять множинні БГА, де одночасно може виконуватися більше ніж одна адресна операція — це дає подальше збільшення продуктивності завдяки суперскалярній природі нових моделей процесорів. Наприклад, мікроархітектури Intel Sandy Bridge і Haswell містять кілька БГА, які збільшують пропускну спроможність підсистеми пам'яті процесора, дозволяючи декілька інструкцій доступу до пам'яті, які будуть виконані паралельно.[4][5][6]

Див. також

- Арифметико-логічний пристрій — цифрова схема, яка виконує арифметичні і логічні операції бітових операцій над цілими двійковими числами

- Bulldozer (мікроархітектура) — ще один процесор з мікроархітектурою, що включає в себе кілька БГА, розроблених AMD

- Перейменування регістрів — метод, який повторно використовує регістри процесора і дозволяє уникнути непотрібних серіалізаций програмних операцій

- Reservation station — це функція процесора, що дозволяє результати різних операцій використовувати в обхід регістрів процесора

Примітки

- Cornelis Van Berkel; Patrick Meuwissen (2006-01-12.mdy.2022). Address generation unit for a processor (US 2006010255 A1 patent application). google.com. Процитовано 2014-12-08.mdy.2022.

- Chapter 4: Address Generation Unit (DSP56300 Family Manual) (PDF). ecee.colorado.edu. 1999-09-16.mdy.2022. Процитовано 2014-12-08.mdy.2022.

- Darek Mihocka (2000-12-27.mdy.2022). Pentium 4: Round 1 Intel blows the lead. emulators.com. Процитовано 2014-12-08.mdy.2022.

- David Kanter (2010-09-25.mdy.2022). Intel’s Sandy Bridge Microarchitecture: Memory Subsystem. realworldtech.com. Процитовано 2014-12-08.mdy.2022.

- David Kanter (2012-11-13.mdy.2022). Intel’s Haswell CPU Microarchitecture: Haswell Memory Hierarchy. realworldtech.com. Процитовано 2014-12-08.mdy.2022.

- Per Hammarlund (August 2013). Fourth-Generation Intel Core Processor, codenamed Haswell (PDF). hotchips.org. с. 25. Архів оригіналу за 5 липня 2016. Процитовано 2014-12-08.mdy.2022.

Посилання

- Блок генерації адрес у сім'ї Motorola DSP56K, Червень 2003, Motorola

- Новий підхід до дизайну AGU в процесорі DSP, Листопад 2011, Kabiraj Sethi та Rutuparna Panda

- Блок генерації адреси у додатках DSP, Вересень 2013, Andreas Ehliar

- Комп'ютерні науки з азів, Частина 3. Архітектура комп'ютера, Вересень 2013, Ian Wienand