Арифметико-логічний пристрій

Арифметико-логічний пристрій (АЛП) (англ. Arithmetic Logic Unit, ALU) — блок процесора, що служить для виконання арифметичних та логічних перетворень над даними, що іменуються операндами[1]. Цей пристрій є фундаментальною частиною будь-якого обчислювача, навіть найпростіші мікроконтролери мають його в складі свого ядра.

Центральний процесор та відеопроцесор можуть мати кілька АЛП, що відрізняються своїм функціональним призначенням або типом оброблюваних даних.

Історія

Концепція АЛП була запропонована математиком Джоном фон Нейманом 1945, коли він працював над новим комп'ютером — EDVAC (англ. Electronic Discrete Variable Computer). В його публікації була досить докладно розглянута структура обчислювальної системи, в якій знайшлося місце для арифметичного пристрою[2]. Фон Нейман зазначав, що наявність цього компонента є гарантією того, що комп'ютер здатний виконувати базові математичні операції, серед яких додавання, віднімання, множення та ділення.

Дослідження АЛП залишається важливою частиною комп'ютерної науки, що підпадають під арифметичні і логічні структури в системі класифікації ACM.

Класифікація

Арифметико-логічні пристрої можуть класифікуватися за багатьма ознаками[3]:

За структурою

- з розподіленою логікою (з закріпленими мікроопераціями);

- з зосередженою логікою (з загальними мікроопераціями).

В першому випадку, апаратура для реалізації обчислень закріплена за регістрами та розділена між ними, тобто кожен з них використовує власну логіку для виконання операцій. У пристроях другого типу вся апаратура об'єднана в АЛП, а всі регістри — в регістровому файлі.

АЛП другого типу також можна класифікувати:

За типом запису даних

- послідовні;

- паралельні;

- послідовно-паралельні.

В основу цієї класифікації покладено особливості роботи цифрового регістра.

За архітектурними особливостями

- з двоспрямованою шиною та одноадресним регістровим файлом;

- з односпрямованою шиною та одноадресним регістровим файлом;

- з односпрямованою шиною та двоадресним регістровим файлом.

Використання двоадресного блоку регістрів чи шини дозволяє збільшити швидкодію, адже запис та читання даних може відбуватися одночасно.

За формою подання даних

- з фіксованою комою;

- з рухомою комою;

- універсальні.

В деяких ЕОМ передбачається спеціальний режим цілих чисел, за якого кома фіксується за останнім розрядом.

За основою системи числення операндів

Окрім наведених, можливі й варіанти АЛП, що працюють в системах числення з основою 2k, де k — додатне ціле число.

Залежно від часу виконання операцій

- синхронного типу;

- асинхронного типу;

- комбінованого типу.

На виконання всіх обчислень в синхронних АЛП відводиться один і той самий час. Проте в асинхронних, витрачається стільки тактів, скільки потрібно, а наступна операція почне виконуватись лише після сигналу про завершення поточної. Комбіновані були створенні для поєднання простоти та швидкодії і поділяють всі операції на дві групи — одно- та багатотактні. Операції першої групи виконуються за синхронним принципом, а другої — асинхронним.

Залежно від реалізації мікроалгоритму

- зі схемним керуванням;

- з мікропрограмним керуванням.

Виконання цих операцій зводиться до виконання послідовності мікрооперацій на регістрах, суматорах та інших цифрових схемах, що входять до складу АЛП. Послідовність мікрооперацій, що приводить до виконання операцій, називають мікроалгоритмом.

Структура

Кожен АЛП може бути представлений як композиція пристрою управління, що керує та операційним пристроєм, що безпосередньо виконує операції. Інколи окремо виділяють блок контролю, що слідкує за правильністю виконання операцій[4]. Якщо пристрій має зосереджену логіку, то до цих компонентів додаються ще й регістри.

Пристрій управління

Якщо АЛП має схемне керування, то його пристрій управління реалізується у вигляді цифрового автомату, що створює відповідні керуючі сигнали залежно від операції. Інакше, пристрій управління реалізується у вигляді комбінаційної схеми разом з постійним запам'ятовуючим пристроєм, що зберігає мікроалгоритм виконання кожної операції. В сучасних АЛП можуть використовуватися обидва підходи[4].

Операційний пристрій

Операційний пристрій, зазвичай, складається з суматора та логічної схеми, що формує признаки результатів операцій, наприклад значення вихідного переносу, нульового результату та інші, що потім об'єднуються в регістрі стану[4].

Регістри

Всередині АЛП можуть перебувати регістри для операндів, результату і стану[4]. Інколи до них додають спеціалізовані індексні та регістри для збереження проміжних обчислень. Деякі з них, наприклад акумулятор, можуть бути доступними програмісту.

Набір операцій

Однією з найважливіших характеристик будь-якого АЛП є набір операцій, що може виконуватися. Він має бути функціонально повним, щоб запрограмувати алгоритм, проте з метою підвищення швидкодії та спрощення програмування, вказаний набір має значну надлишковість[3]. Кількість операцій може значно коливатися, наприклад від кількох десятків до кількох сотень, проте зазвичай це число відповідає степені двійки.

До найбільш поширених зараховують операції[4]:

- встановлення константи;

- інвертування;

- конкатенація даних;

- переміщення операндів між регістрами;

- додавання;

- збільшення (інкремент) чи зменшення (декремент) на одиницю (що є зручним для організації циклів);

- порозрядні (бітові) логічні (булеві) операції: кон'юнкція, диз'юнкція, виключна диз'юнкція тощо;

- логічні, арифметичні та циклічні зсуви або ротації вліво чи вправо.

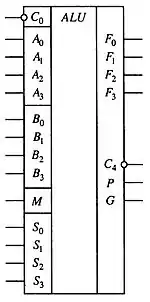

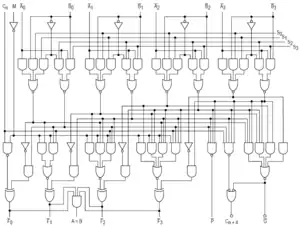

Система команд типового представника АЛП — мікросхеми 74181[5]:

|

Структура мікросхеми 74181 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

Реалізація

Розрядність пристрою сильно впливає на розрядність процесора, зазвичай вони збігаються. Проте через конструктивні особливості (кількість ніжок мікросхеми), АЛП, що випускаються в складі серій цифрових мікросхем, оперують 4-розрядними даними. Аби подолати це обмеження, застосовують прискорений груповий перенос (англ. group-carry lookahead)[5]. Таким чином можна сконструювати пристрій будь-якої розрядності.

Примітки

- Ланский, Александр (4 липня 2019). Как работает процессор?. Tproger (ru-RU). Процитовано 4 грудня 2020.

- Burks, A. W., Goldstine, H. H., von Neumann, J. Preliminary discussion of the logical design of an electronic computing instrument, 1945

- Жабін В. І., Жуков В. А., Клименко І. А., Стіренко С. Г. Арифметичні та управляючі пристрої цифрових ЕОМ: Навчальний посібник. — К.: ВЕК+, 208. — 176 с. — ISBN 966-7140-11-3

- Бабич Н. П., Жуков И. А. Компьютерная схемотехника. Методы построения и проектирования: Учебное пособие. — К.: «МК-Пресс», 2004. — 576 с., илл. — ISBN 966-96415-2-7. (рос.)

- John F. Wakerly Digital Design: Principles and Practices. — 4th Edition, 2005. — ISBN 0-13-186389-4 (англ.)

Література

- Лехин С. Н. Схемотехника ЭВМ. — Спб.: БХВ-Петербург, 2010. — 672 с.: ил. — ISBN 978-5-9775-0353-2. (рос.)

- Процюк Р. О., Корнейчук В. И., Кузьменко П. В., Тарасенко В. П. Компьютерная схемотехника (краткий курс). — К.: «Корнійчук», 2006. — 433 с. — ISBN 966-7599-38-8. (рос.)