Мережа на чипі

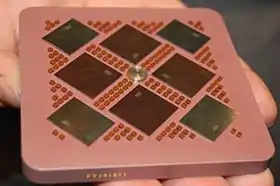

Мережа на чипі чи мережі на чипі (англ. Network on Chip, NoC або NOC) — методологія проектування багатоядерних інтегральних схем (багаточипових модулів) для створення систем на кристалі (англ. System on chip, SoC) як сукупності чиплетів або ядер інтелектуальної власності (англ. Intellectual Property, IP) та підсистеми зв'язку між ними.

NoCs може охоплювати синхронні та асинхронні домени синхрочастот або використовувати асинхронну логіку. NoC покращує масштабованість SoC, а також енергетичну ефективність складних SoC у порівнянні з іншими конструкціями.

Паралельність та масштабованість

Високий рівень паралелізму в NoC досягається завдяки тому, що усі її вузли можуть працювати одночасно з різними пакетами даних. Тому, оскільки складність інтегрованих систем продовжує зростати, NoC забезпечує підвищену продуктивність (наприклад, пропускну здатність) і масштабованість у порівнянні з попередніми архітектурами зв'язку (наприклад, спеціальні сигнальні дротові з'єднання "точка-точка", спільні комп'ютерні шини або сегментовані комп'ютерні шини з мостами). Звичайно, алгоритми повинні бути розроблені таким чином, щоб вони пропонували великий паралелізм і, отже, могли використовувати потенціал NoC.

Переваги

Традиційно інтегральні схеми проектувалися з віддаленими точками з'єднання, з одним проводом, присвяченим кожному сигналу. Для систем на кристалі це має ряд обмежень з точки зору фізичного дизайну, оскільки дроти займають більшу частину площі мікросхеми. В технології NoC на основі нанометрового КМОП покращується як продуктивність, так і динамічна потужність з урахуванням того, що поширення сигналу в проводах на чипі вимагає кількох тактових циклів.

Дослідження мереж на чипі

.PNG.webp)

Технологія NoC застосовує мережеві теорії та методи комунікації на чипі та забезпечує помітні покращення у порівнянні з звичайними комп'ютерними шинами і перехресними з'єднаннями. Деякі дослідники вважають, що NoCs повинні підтримувати якість обслуговування (QoS), а саме досягнення різних вимог з точки зору пропускної спроможності, кінцевих затримок, справедливості та ліміту часу. Однією з причин надання підтримки QoS є обчислення в режимі реального часу, включаючи відтворення аудіо та відео. Тим не менш, поточні реалізації системи, такі як VxWorks, RTLinux або QNX, дозволяють досягти обчислень в режимі реального часу без спеціального устаткування. Це може свідчити про те, що для багатьох застосунків у режимі реального часу достатньою є якість обслуговування наявної інфраструктури внутрішнього з'єднання. Ще однією мотивацією до якості сервісу на рівні чипсетів є підтримка їх множини з поділом ресурсів багатоядерного чипу у загальнодоступній інфраструктурі обчислень. У таких випадках апаратна QOS логіка дає змогу надавати гарантії на рівень сервісу, який отримує чипсет.

Перший спеціалізований науково-дослідний симпозіум з мереж на чипі було проведено в Принстонському університеті в травні 2007 року[1]. Другий IEEE Міжнародний симпозіум з мереж на чипі відбувся у квітні 2008 року в Ньюкаслському університеті.

Основними проблемами, що на них обговорювалися, були високі часові затримки передачі сигналів і енергетичні втрати у розгалуженій мережі ланцюгів при реалізації NoC за традиційною 2D топологією. Для розв'язання цих проблем пропонувалися різні методи — використання радіочастотних і оптичних хвилеводних ліній, а також тривимірної архітектури NoC[2]. Зокрема, було проведено дослідження інтегральних оптичних хвилеводів для створення оптичних мереж на чипі (ONoC)[3][4].

Однак усі ці технології мають серйозні недоліки. Висока інтеграція елементів NoC в тривимірному виконанні ускладнює відведення тепла з центральних областей чипсету та погіршує температурний режим при роботі на високих частотах. Завдання розміщення в SoC великої кількості оптичних хвилеводів і інтегрованих оптоелектронних пристроїв лишається технологічно складним, а для досягнення високої пропускної здатності радіочастотних ліній передачі необхідно мати масив високочастотних генераторів і фільтрів[2]. Для подолання цих проблем було запропоновано бездротовий принцип передачі сигналів в NoC з використанням бездротових мереж на чипі (англ. Wireless Network on Chip, WiNoC)[2].

При цьому може бути використано ємнісний або індуктивний зв'язок між шарами 3D чипсету та радіозв'язок між окремими ядрами SoC у тому числі за принципом MIMO[2].

Тестування

Розробка та дослідження NoC вимагають порівняння різних пропозицій та варіантів. Тому моделі NoC розробляються, щоб допомогти таким оцінкам. Існуючі контрольні показники «NoC» включають NoCBench та MCSL NoC Traffic Patterns[5].

IPU

Важливим елементом NoC є блок обробки з'єднання (англ. Interconnect processing unit, IPU)[6]. По суті, він забезпечує управління он-лайн мережею зв'язку (NoC) з апаратними та програмними компонентами, які спільно реалізують ключові функції різних моделей програмного забезпечення SoC за допомогою набору комунікаційних та синхронізованих примітивів і надають послуги платформи низького рівня.

Комерційні постачальники

Див. також

- Electronic design automation (EDA)

- Integrated circuit design

- MPSoC

- manycore

- Система на кристалі

Примітки

- NoCS 2007 website.

- Слюсар, Д.; Слюсар, В. (2011). Беспроводные сети на кристалле – перспективные идеи и методы реализации. Электроника: наука, технология, бизнес. 6: 74 – 83.

- On-Chip Networks Bibliography

- Inter/Intra-Chip Optical Network Bibliography-

- MCSL NoC Traffic Patterns

- Marcello Coppola, Miltos D. Grammatikakis, Riccardo Locatelli, Giuseppe Maruccia, Lorenzo Pieralisi, «Design of Cost-Efficient Interconnect Processing Units: Spidergon STNoC», CRC Press, 2008, ISBN 978-1-4200-4471-3

Посилання

- DATE 2006 workshop on NoC

- NoCS 2007 — The 1st ACM/IEEE International Symposium on Networks-on-Chip

- NoCS 2008 — The 2nd IEEE International Symposium on Networks-on-Chip

- Cristian Grecu, Andrè Ivanov, Partha Pande, Axel Jantsch, Erno Salminen, Umit Ogras, Radu Marculescu, An Initiative towards Open Network-on-Chip Benchmarks, OCP-Ip white paper, 2007, [Online] http://www.ocpip.org/uploads/documents/NoC-Benchmarks-WhitePaper-15.pdf

- Jean-Jacques Lecler, Gilles Baillieu, Design Automation for Embedded Systems (Springer), «Application driven network-on-chip architecture exploration & refinement for a complex SoC», June 2011, Volume 15, Issue 2, pp 133—158, doi:10.1007/s10617-011-9075-5 [Online] http://www.arteris.com/hs-fs/hub/48858/file-14363521-pdf/docs/springer-appdrivennocarchitecture8.5x11.pdf