КМОН

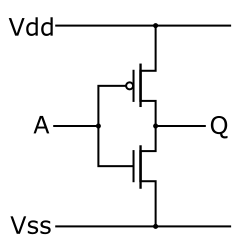

КМОН структура або КМОН транзистор (комплементарна структура метал-оксид-напівпровідник; англ. CMOS, Complementary-symmetry/metal-oxide semiconductor) — являє собою вид технічного процесу виготовлення польового МОН — транзистора (англ. MOSFET), що використовує симетричні комплементарні пари МОН транзисторів p-типу та n-типу для реалізації логічних функцій.[1] Технологія КМОН використовується для побудови інтегральних мікросхем (ІС), таких як мікропроцесори, мікроконтролери, мікросхеми пам'яті та інші цифрові логічні схеми. Технологія КМОН використовується також для аналогових схем, таких як датчики зображення, перетворювачі даних, радіочастотні схеми та високо інтегровані приймачі для багатьох типів зв'язку.

Основною особливістю схем КМОН в порівнянні з біполярними технологіями є дуже мале енергоспоживання в статичному режимі (здебільшого можна вважати, що енергія споживається тільки під час перемикання станів) у випадку послідовного їх з'єднання (наприклад, у вигляді інвертора, чи якоїсь іншої логічної схеми).

Другою особливістю структури КМОН в порівнянні з іншими МОН-структурами (N-МОН або англ. NMOS , P-МОН або англ. PMOS) є наявність як n-, так і p-канальних польових транзисторів на одній напівпровідниковій підкладці; як наслідок, КМОН-схеми мають вищу швидкодію та менше енергоспоживання, проте при цьому характеризуються складнішим технологічним процесом виготовлення і меншою щільністю упаковки.

Історія

МДН транзистор (або МОН транзистор або англ. MOSFET) винайшли Мохамед М. Атала та Доун Канг у Bell Labs у 1959 році. Спочатку було два типи процесу виготовлення: P-МОН (p-тип МОН) та N-МОН (n-тип МОН).[2] Обидва типи були розроблені Аталою та Кангом, коли вони спочатку винайшли МОН-польовий транзистор, виготовляючи як p-канальні, так і n-канальні транзистори за 20 мкм процесом в 1960 році.[3] Хоча у Bell Labs спочатку не помічали КМОН транзисторів та ігнорували їх віддаючи першість біполярним транзисторам,[3] винахід МДН транзистора викликало значний інтерес у Fairchild Semiconductor .[2] Базуючись на роботі Атали,[4] Са Чжітан впровадив технологію МОН для Fairchild Semiconductor з його контрольованим МОН — тетродом, виготовленим наприкінці 1960 року.[2]

Са Чжітан та Френк Ванлас розробили новий тип логіки на МДН транзисторах, що поєднує у собі обидва процеси P-МОН і N-МОН, що називається комплементарною парою МОН (англ. CMOS). У лютому 1963 р. Вони опублікували свій винахід у науковій роботі .[5][6] Пізніше Ванлас подав документи на патент США 3 356 858 схеми КМОН у червні 1963 року, який був виданий у 1967 році. Як у дослідницькій роботі, так і в патенті було описано виготовлення приладів КМОН на основі термічного окислення кремнійорганічної підкладки для отримання шару діоксиду кремнію, розташованого між точкою з'єднання стоку та витоку транзисторів.[7][6]

КМОН був комерціалізований в кінці 1960-х. Цю технологію було прийнято для проектування інтегральних мікросхем (ІС), розробляючи схеми КМОН для комп'ютера ВПС у 1965 році, а потім 288- бітний чіп пам'яті CMOS SRAM в 1968 році.[8] Також КМОН використовувався для інтегральних мікросхем серії 4000 в 1968 році, починаючи з 20 мкм процесу виготовлення напівпровідників. Згодом, поступово процес масштабували до 10 мкм протягом наступних кількох років.[9]

Американська індустрія напівпровідників спочатку не помічала технологію КМОН, віддаючи перевагу N-КМОН, яка була на той час більш розвиненою. Однак КМОН було швидко прийнято і вдосконалено японськими виробниками напівпровідників завдяки низькому енергоспоживанню, що призвело до зростання японської промисловості напівпровідників.[10] У 1969 році Toshiba розробила C²MOS (Clocked CMOS), технологію з меншим споживанням енергії та більшою швидкодією, ніж звичайний CMOS. Toshiba використовувала свою технологію C²MOS у розробці мікросхеми для кишенькового калькулятора Sharp EL-801 Elsimini, розробленого в 1971 році і випущеного в 1972 році[11] Suwa Seikosha (нині Seiko Epson) розпочала розробку мікросхеми CMOS для кварцових годинників Seiko в 1969 році, а в 1971 році Seiko розпочала серійне виробництво годинника Analog Quartz 38SQW.[12] Першим масовим електронним продуктом з технологією CMOS був цифровий годинник Hamilton Pulsar «Wrist Computer», випущений у 1970 році.[13] Через низьке енергоспоживання логіка CMOS широко застосовується для калькуляторів і годинників з 1970-х років.[14]

Найпершими мікропроцесорами на початку 1970-х були процесори PMOS, які спочатку домінували в ранній мікропроцесорній галузі. До кінця 1970-х мікропроцесори NMOS випередили процесори PMOS. Однак процесори CMOS не стали домінуючими аж до 1980-х.[15]

CMOS спочатку був повільнішим за логіку N-МОН, тому N-МОН в 1970-х роках широко використовувався для комп'ютерів.[16] Intel 5101 (1 kb SRAM) чіп пам'яті CMOS (1974) мав час доступу 800 нс,[17][18] тоді як найшвидший чіп NMOS на той час, Intel 2147 (4 kb SRAM) мікросхема пам'яті HMOS (1976), час доступу 55/70 нс.[16][18] У 1978 р. Дослідницька команда Hitachi під керівництвом Тошіакі Масухари представила процес Hi-CMOS у мікросхемі пам'яті HM6147 (4 kb SRAM), виготовленою за 3 мкм процесом .[16][19][20] Чіп Hitachi HM6147 зміг зрівнятися за швидкодією (55/70 нс доступ) з чіпом Intel 2147 HMOS, однак HM6147 витрачав значно менше енергії (15 мА), проти Intel 2147 (110 мА). Маючи однакову продуктивність та набагато менше енергоспоживання, процес C²MOS зрештою обігнав NMOS і став найпоширенішим техпроцесом виготовлення напівпровідників для комп'ютерів у 1980-х.[16]

У 1980-х мікропроцесори CMOS випередили мікропроцесори NMOS.[21] Космічний корабель NASA Galileo, відправлений на орбіту Юпітера в 1989 році, використовував мікропроцесор RCA 1802 CMOS завдяки його низькому енергоспоживанню.[22]

Компанія Intel запропонувала 1,5 мкм процес виготовлення напівпровідникових пристроїв CMOS в 1983 році.[23] У середині 1980-х Біджан Даварі із IBM розробив високоефективну низьковольтну технологію CMOS з нанометровим техпроцесом, що дало розвиток більш швидким комп'ютерам, портативним комп'ютерам та мобільним пристроям.[24] У 1988 році Даварі очолив команду IBM, яка продемонструвала високоефективний 250 нанометровий техпроцес CMOS.[25]

Fujitsu комерціалізував 700 нм техпроцес CMOS в 1987 році[26] а потім Hitachi, Mitsubishi Electric, NEC і Toshiba комерціалізували 500 нм CMOS у 1989 р.[27] У 1993 році компанія Sony продала 350 нм CMOS-процес, в той час як Hitachi і NEC продали 250 нм CMOS. Hitachi представив 160 нм техпроцес CMOS в 1995 році, тоді Mitsubishi представила 150 нм CMOS в 1996 році, а потім Samsung Electronics представив 140 нм у 1999 р.[27]

У 2000 році у компанії Micron Technology винайшли атомно-шарове осадження плівок діелектрика з діелектричною проникністю більшою, ніж у діоксида кремнію (High-k технологія), що призвело до розробки економічно ефективного процесу CMOS 90 нм .[28][29] Toshiba та Sony розробили 65 нм техпроцес CMOS у 2002 році[30] а потім TSMC ініціював розробку логіки CMOS з техпроцесом 45 нм у 2004 році.[31] Розвиток технології багатошарової літографії призвів до появи 30 нм техпроцесу CMOS у 2000-х роках.[28]

CMOS використовується в більшості сучасних мікросхем та інтегрованих схемах надвеликого рівня інтеграції (VLSI) .[32] З 1976 по 2010 рік, процесори з найкращою продуктивністю на ват були виготовлені за CMOS технологією статичної логіки. Станом на 2019 рік, планарна CMOS-технологія все ще є найпоширенішою формою виготовлення напівпровідникових пристроїв, але поступово її замінює непланарна технологія FinFET, за якою можна виготовляти напівпровідникові прилади менше 20 нм .[33]

Див. також

Примітки

- What is CMOS Memory?. Wicked Sago. Архів оригіналу за 26 вересня 2014. Процитовано 3 березня 2013.

- 1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated. The Silicon Engine: A Timeline of Semiconductors in Computers. Computer History Museum. Процитовано 31 серпня 2019.

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. с. 321–3. ISBN 9783540342588.

- Sah, Chih-Tang (October 1988). Evolution of the MOS transistor-from conception to VLSI. Proceedings of the IEEE 76 (10): 1280–1326 (1290). ISSN 0018-9219. doi:10.1109/5.16328. «Those of us active in silicon material and device research during 1956 – 1960 considered this successful effort by the Bell Labs group led by Atalla to stabilize the silicon surface the most important and significant technology advance, which blazed the trail that led to silicon integrated circuit technology developments in the second phase and volume production in the third phase.»

- 1963: Complementary MOS Circuit Configuration is Invented. Computer History Museum. Процитовано 6 липня 2019.

- Sah, Chih-Tang; Wanlass, Frank (1963). Nanowatt logic using field-effect metal-oxide semiconductor triodes. 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers VI: 32–33. doi:10.1109/ISSCC.1963.1157450.

- Low stand-by power complementary field effect circuitry

- 1963: Complementary MOS Circuit Configuration is Invented. Computer History Museum. Процитовано 6 липня 2019.

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. с. 330. ISBN 9783540342588.

- Gilder, George (1990). Microcosm: The Quantum Revolution In Economics And Technology. Simon and Schuster. с. 144–5. ISBN 9780671705923.

- 1972 to 1973: CMOS LSI circuits for calculators (Sharp and Toshiba). Semiconductor History Museum of Japan. Процитовано 5 липня 2019.

- Early 1970s: Evolution of CMOS LSI circuits for watches. Semiconductor History Museum of Japan. Процитовано 6 липня 2019.

- Tortoise of Transistors Wins the Race - CHM Revolution. Computer History Museum. Процитовано 22 липня 2019.

- 1978: Double-well fast CMOS SRAM (Hitachi). Semiconductor History Museum of Japan. Процитовано 5 липня 2019.

- Kuhn, Kelin (2018). CMOS and Beyond CMOS: Scaling Challenges. High Mobility Materials for CMOS Applications. Woodhead Publishing. с. 1. ISBN 9780081020623.

- 1978: Double-well fast CMOS SRAM (Hitachi). Semiconductor History Museum of Japan. Процитовано 5 липня 2019.

- Silicon Gate MOS 2102A. Intel. Процитовано 27 червня 2019.

- A chronological list of Intel products. The products are sorted by date. (PDF). Intel museum. Intel Corporation. July 2005. Архів оригіналу за August 9, 2007. Процитовано 31 липня 2007.

- Masuhara, Toshiaki; Minato, Osamu; Sasaki, Toshio; Sakai, Yoshio; Kubo, Masaharu; Yasui, Tokumasa (February 1978). A high-speed, low-power Hi-CMOS 4K static RAM. 1978 IEEE International Solid-State Circuits Conference. Digest of Technical Papers XXI: 110–111. doi:10.1109/ISSCC.1978.1155749.

- Masuhara, Toshiaki; Minato, Osamu; Sakai, Yoshi; Sasaki, Toshio; Kubo, Masaharu; Yasui, Tokumasa (September 1978). Short Channel Hi-CMOS Device and Circuits. ESSCIRC 78: 4th European Solid State Circuits Conference - Digest of Technical Papers: 131–132.

- Kuhn, Kelin (2018). CMOS and Beyond CMOS: Scaling Challenges. High Mobility Materials for CMOS Applications. Woodhead Publishing. с. 1. ISBN 9780081020623.

- Tortoise of Transistors Wins the Race - CHM Revolution. Computer History Museum. Процитовано 22 липня 2019.

- Gealow, Jeffrey Carl (10 серпня 1990). Impact of Processing Technology on DRAM Sense Amplifier Design. CORE. Massachusetts Institute of Technology. с. 149–166. Процитовано 25 червня 2019.

- IEEE Andrew S. Grove Award Recipients. IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Процитовано 4 липня 2019.

- Davari, Bijan (1988). A high-performance 0.25 micrometer CMOS technology. International Electron Devices Meeting.

- Gealow, Jeffrey Carl (10 серпня 1990). Impact of Processing Technology on DRAM Sense Amplifier Design. CORE. Massachusetts Institute of Technology. с. 149–166. Процитовано 25 червня 2019.

- Memory. STOL (Semiconductor Technology Online). Процитовано 25 червня 2019.

- IEEE Andrew S. Grove Award Recipients. IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Процитовано 4 липня 2019.

- Sandhu, Gurtej; Doan, Trung T. (22 серпня 2001). Atomic layer doping apparatus and method. Google Patents. Процитовано 5 липня 2019.

- Toshiba and Sony Make Major Advances in Semiconductor Process Technologies. Toshiba. 3 грудня 2002. Процитовано 26 червня 2019.

- A Banner Year: TSMC Annual Report 2004. TSMC. Процитовано 5 липня 2019.

- 1978: Double-well fast CMOS SRAM (Hitachi). Semiconductor History Museum of Japan. Процитовано 5 липня 2019.

- Global FinFET Technology Market 2024 Growth Analysis by Manufacturers, Regions, Type and Application, Forecast Analysis. Financial Planning. 3 липня 2019. Процитовано 6 липня 2019.

Література

- Baker, R. Jacob (2008). CMOS: Circuit Design, Layout, and Simulation, Revised Second Edition. Wiley-IEEE. ISBN 978-0-470-22941-5. http://CMOSedu.com/

- Weste, Neil H. E., Harris, David M. (2005). CMOS VLSI Design: A Circuits and Systems Perspective, Third Edition. Boston: Pearson/Addison-Wesley. ISBN 0-321-26977-2.

- Carver Mead й Lynn Conway (1980). Introduction to VLSI systems. Boston: Addison-Wesley. ISBN 0-201-04358-0.