AMD K10

K10 — x86 сумісна мікроархітектура центрального процесора, розроблена корпорацією Advanced Micro Devices.

| Роки виробництва: | з кінця 2007 по нині |

|---|---|

| Виробник(и): | Advanced Micro Devices |

| Макс. частота CPU: | 1700 МГц – 3700 МГц |

| Частота FSB: | 1000 МГц – 2000 МГц |

| Техпроцес: | 65 нм – 45 нм |

| Набір команд: | x86-64 |

| Попередник: | AMD K8 |

| Наступник: | Bulldozer |

| Роз'єм(и): | |

| Назва ядра: |

Перша згадка про мікроархітектуру наступного покоління з'явилося в 2003 році, на форумі Microprocessor Forum 2003. На ньому зазначалося, що в нову мікроархітектуру буде покладена багатоядерність процесорів, які будуть працювати на тактових частотах до 10 ГГц. Пізніше тактові частоти були в кілька разів занижені. Перші офіційні згадки AMD про розробку чотириядерних процесорів з'явилися в травні 2006 в дорожній карті до 2009 року.

Правда, тоді нова мікроархітектура значилася під кодовим найменуванням AMD K8L, і тільки в лютому 2007 року було затверджено остаточне найменування AMD K10.

Процесори, засновані на поліпшеній архітектурі AMD K8, повинні були стати першими чотириядерними процесорами AMD, а також першими процесорами на ринку, в якому всі 4 ядра розташовані на одному кристалі (раніше ходили чутки про появу чотириядерного процесора AMD, що являє собою два двоядерних кристали Opteron). Інші особливості: поновлення протоколу Hyper-Transport до версії 3.0, загальний для всіх ядер кеш L3, а також перспективна підтримка контролером пам'яті DDR3. Самі ядра також були модернізовані в порівнянні з ядрами AMD K8.

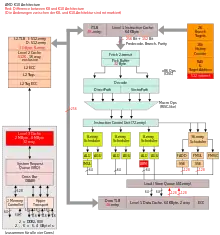

Архітектура Direct Connect Architecture

- Дозволяє збільшити продуктивність і ефективність шляхом прямого з'єднання контролера пам'яті і каналу введення / виводу з ядром.

- Розроблена для одночасного виконання як 32-бітових, так і 64-бітових обчислень.

- Інтеграція контролера пам'яті стандарту DDR2 (аж до режиму 533 (1066) МГц, а також з перспективною підтримкою DDR3)

Переваги:

- Збільшення продуктивності додатків шляхом скорочення затримок при зверненні до пам'яті

- Розподіляє смугу пропускання пам'яті залежно від запитів

- Технологія Hyper-Transport забезпечує з'єднання на піковій швидкості до 16,0 ГБ/с для запобігання затримок

AMD Balanced Smart Cache

Загальний для всіх ядер кеш L3 об'ємом 2 МБ на додаток до 512 КБ кешу L2 для кожного ядра. Перевага — скорочення затримок при зверненні до часто використовуваних даних для збільшення продуктивності.

AMD Wide Floating Point Accelerator

128-бітний FPU для кожного ядра. Перевага — прискорення вибірки та обробки даних в обчисленнях з рухомою комою.

HyperTransport

- Один 16-бітний канал зі швидкістю 4000 Mt / s

- З'єднання Hyper-Transport з піковою швидкістю до 8,0 ГБ / с і до 16,0 ГБ / с при роботі в режимі Hyper-Transport 3.0

- До 33,1 ГБ /с сумарної пропускної спроможності між процесором і системою (з урахуванням шини Hyper-Transport і контролера пам'яті)

Перевага — швидкий доступ до системних ресурсів для збільшення продуктивності

Інтегрований контролер пам'яті

- Інтегрований контролер пам'яті з високою пропускною здатністю і низькими затримками

- Підтримка PC2-8500 (DDR2-1066); PC2-6400 (DDR2-800), PC2-5300 (DDR2-667), PC2-4200 (DDR2-533) і PC2-3200 (DDR2-400) небуферізованних модулів пам'яті

- Підтримка 64-бітної DDR2 SDRAM

- Пропускна здатність до 17.1 Гб / с.

Перевага — швидкий доступ до системних ресурсів для збільшення продуктивності

AMD-V

Технологія апаратної віртуалізації x86, схожа на Intel VT-x, але повністю несумісна з нею. Доповнення до AMD-V називається Rapid Virtualization Indexing.

Cool'n'Quiet 2.0

- Удосконалена система управління живленням, автоматично регулююча продуктивність процесора залежно від навантаження

- Зниження споживання енергії і швидкості обертання кулера в режимі простою

CoolCore

- Дозволяє знижувати енергоспоживання шляхом відключення невикористовуваних частин процесора.

- Роздільна система для контролера пам'яті і логіки процесора дозволяє керувати напругою і відключати їх незалежно один від одного

- Працює автоматично без необхідності підтримки з боку драйвера або BIOS

- Дозволяє незалежно управляти частотами кожного ядра

- Швидкість перемикання режимів роботи дорівнює одному такту процесорного ядра

TLB bug

Щодо процесорів Agena і Barcelona (AMD) часто згадується так званий TLB bug, або помилка TLB. Дана помилка зустрічається у всіх чотириядерних процесорах AMD ревізії B2 і може привести в дуже рідкісних випадках до непередбачуваної поведінки системи при високих навантаженнях. Дана помилка критична в серверному сегменті, що стало причиною припинення всіх поставок процесорів Barcelona (AMD) ревізії В2. Для настільних процесорів Phenom був запропонований TLB patch який запобігає виникненню помилки шляхом відключення частини логіки TLB. Даний патч, хоч і рятує від TLB bug але також негативно впливає на продуктивність. Помилка виправлена в ревізії B3.

TDP і ACP

З виходом процесорів Opteron 3G на ядрі Barcelona компанія AMD ввела нову енергетичну характеристику під назвою ACP (Average CPU Power) — середній рівень енергоспоживання нових процесорів при навантаженні. AMD також продовжить вказувати і максимальний рівень енергоспоживання — TDP.