Технологія виробництва напівпровідників

Технологічний процес напівпровідникового виробництва — технологічний процес виготовлення напівпровідникових (н/п) виробів і матеріалів, що складається з послідовності технологічних (обробка, складання) та контрольних операцій, частина виробничого процесу виготовлення н/п виробів (транзисторів, діодів тощо).

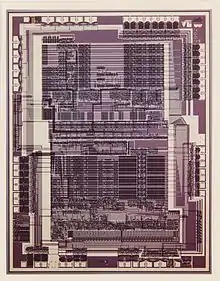

При виробництві н/п інтегральних мікросхем застосовується фотолітографія і літографічне обладнання. Роздільна здатність (у мкм і нм) цього обладнання (т. зв. Проектні норми) і визначає назву застосовуваного конкретного технологічного процесу.

Удосконалення технології та пропорційне зменшення розмірів н/п структур сприяють поліпшенню характеристик (розміри, енергоспоживання, вартість) напівпровідникових приладів (мікросхем, процесорів, мікроконтролерів тощо). Особливу значимість це має для процесорних ядер, в аспектах споживання електроенергії та підвищення продуктивності, тому нижче вказані процесори (ядра) масового виробництва на даному техпроцесі.

Особливості

Технології виробництва напівпровідникової продукції з субмікронними розмірами елементів заснована на надзвичайно широкому колі складних фізико-хімічних процесів: отримання тонких плівок термічним і іонно-плазмовим розпиленням у вакуумі, механічна обробка пластин проводиться по 14-му класу чистоти з відхиленням від площинності не більше 1 мкм, широко застосовується ультразвук і лазерне випромінювання, використовуються відпал у кисні і водні, робочі температури при плавленні металів досягають більше 1500 ° C, при цьому дифузійні печі підтримують температуру з точністю 0,5 ° C, широко застосовуються небезпечні хімічні елементи та з'єднання (наприклад, білий фосфор).

Все це обумовлює особливі вимоги до виробничої гігієни, так звану «електронну гігієну», адже в робочій зоні обробки напівпровідникових пластин або на операціях складання кристала не повинно бути більше п'яти пилинок розміром 0,5 мкм в 1 л повітря. Тому в чистих кімнатах на фабриках з виробництва подібних виробів всі працівники зобов'язані носити спеціальні комбінезони. У рекламних матеріалах Intel спецодяг працівників отримала назву bunny suit («костюм кролика»).

Етапи технологічного процесу

Технологічний процес виробництва напівпровідникових приладів та інтегральних мікросхем (мікропроцесорів, модулів пам'яті та ін) включає нижченаведені операції.

- Механічну обробку напівпровідникових пластин — отримують пластини напівпровідника зі строго заданої геометрією, потрібної кристалографічної орієнтацією (не гірше ± 5 %) і класом чистоти поверхні. Ці пластини надалі служать заготовками у виробництві приладів або підкладками для нанесення епітаксійного шару.

- Хімічну обробку (попередню всім термічним операціями) — видалення механічно порушеного шару напівпровідника і очищення поверхні пластини. Основні методи хімічної обробки: рідинне і газове травлення, плазмохімічні методи. Для отримання на пластині рельєфу (профілізація поверхні) у вигляді виступів і западин певної геометрії, для витравлювання вікон в маскувальних покриттях, для прояву прихованого зображення в шарі експонованого фоторезисту, для видалення його заполімерізірованних залишків, для отримання контактних майданчиків і розведення в шарі металізації застосовують хімічну (електрохімічну) обробку.

- Епітаксіальне нарощування шару напівпровідника — осадження атомів напівпровідника на підкладку, в результаті чого на ній утворюється шар, кристалічна структура якого подібна структурі підкладки. При цьому підкладка часто виконує лише функції механічного носія.

- Отримання маскуючого покриття — для захисту шару напівпровідника від проникнення домішок на наступних операціях легування. Найчастіше проводиться шляхом окислення епітаксійного шару кремнію в середовищі кисню при високій температурі.

- Фотолітографія — виробляється для утворення рельєфу в діелектричній плівці.

- Введення електрично активних домішок в пластину для утворення окремих p- та n-областей — потрібно для створення електричних переходів, ізолюючих дільниць. Проводиться методом дифузії з твердих, рідких або газоподібних джерел, основними дифузантами у кремній є фосфор і бор.

- Термічна дифузія — спрямоване переміщення частинок речовини в бік убування їх концентрації: визначається градієнтом концентрації. Часто застосовується для отримання введення легуючих домішок у напівпровідникові пластини (або вирощені на них епітаксіальні шари) для отримання протилежної, в порівнянні з вихідним матеріалом, типу провідності, або елементів з більш низьким електричним опором.

- Іонне легування (застосовується при виготовленні напівпровідникових приладів з великою щільністю переходів, сонячних батарей і СВЧ-структур) визначається початковою кінетичною енергією іонів в напівпровіднику і виконується в два етапи:

- в напівпровідникову пластину на вакуумній установці вводять іони

- робиться відпал при високій температурі

У результаті відновлюється порушена структура напівпровідника і іони домішки займають вузли кристалічної решітки.

- Отримання омічних контактів і створення пасивних елементів на пластині — за допомогою обробки фотолітографії в шарі оксиду, що покриває області сформованих структур, над попередньо створеними сильно легованими областями n+- або p+-типу, які забезпечують низький перехідний опір контакту, розкривають вікна. Потім, методом вакуумного напилення всю поверхню пластини покривають шаром металу (металізують), надлишок металу видаляють, залишивши його тільки на місцях контактних майданчиків і розводки. Отримані таким чином контакти, для поліпшення адгезії матеріалу контакту до поверхні і зменшення перехідного опору, термічно обробляють (операція відпалу). У разі напилення на матеріал оксиду спеціальних сплавів отримують пасивні тонкоплівкові елементи — резистори, конденсатори, індуктивності.

- Додавання додаткових шарів металу (у сучасних процесах — близько 10 шарів), між шарами розташовують діелектрик (англ. inter-metal dielectric, IMD) з наскрізними отворами.

- Пасивація поверхні пластини. Перед контролем кристалів необхідно очистити їх зовнішню поверхню від різних забруднень. Більш зручною (в технологічному плані) є очищення пластин безпосередньо після скрайбування або різання диском, поки вони ще не розділені на кристали. Це доцільно й тому, що крихти напівпровідникового матеріалу, утворені при скрайбуванні або надрізанні пластин, потенційно є причиною появи браку при розмелюванні їх на кристали з утворенням подряпин при металізації. Найбільш часто пластини очищають у деіонізованій воді на установках гідромеханічної (кістьевой) відмивання, а потім сушать на центрифузі, в термошкафу при температурі не більше 60 ° C або інфрачервоним нагрівом. На очищеній пластині визначаються дефекти вносяться операцією скрайбування і розламування пластин на кристали, а також раніше проведених операціях — фотолітографії, окисленні, напилюванні, вимірі (відколи й мікротріщини на робочій поверхні, подряпини та інші ушкодження металізації, залишки оксиду на контактних майданчиках, різні залишкові забруднення у вигляді фоторезиста, лаку, маркувальної фарби і т. ін.).

- Тестування нерозрізаної пластини. Зазвичай це випробування зондовими головками на установках автоматичної розбракування пластин. У момент торкання зондами розбраковуваних структур вимірюються електричні параметри. У процесі маркуються браковані кристали, які потім відкидаються. Лінійні розміри кристалів зазвичай не контролюють, так як їх висока точність забезпечується механічною та електрохімічною обробкою поверхні (товщина) і наступним скрайбуванням (довжина і ширина).

- Поділ пластин на кристали — механічно поділяє (розрізанням) пластину на окремі кристали.

- Збірка кристала і наступні операції монтажу кристала в корпус і герметизація — приєднання до кристалу виводів і подальша упаковка в корпус, з подальшою його герметизацією.

- Електричні вимірювання та випробування — проводяться з метою відбракування виробів, що мають невідповідні технічної документації параметри. Іноді спеціально випускаються мікросхеми з «відкритим» верхньою межею параметрів, що допускають згодом роботу в позаштатних для решти мікросхем режимах підвищеного навантаження (див., наприклад, Розгін комп'ютерів).

- Тестова структура — гетероструктура, сформована на напівпровідниковій пластині, що використовується у процесі тестового контролю мікросхем на виробництві. Завершальний технологічний цикл виготовлення пристрою — вельми важливе і складне завдання (так, для перевірки всіх комбінацій схеми, що складається з 20 елементів з 75 (сукупно) входами, при використанні пристрою, що працює за принципом функціонального контролю зі швидкістю 104 перевірок у секунду, буде потрібно 1019 років).

- Маркування, нанесення захисного покриття, упаковка — завершальні операції перед відвантаженням готового виробу кінцевому споживачеві.

Технології виробництва напівпровідникової продукції з субмікронними розмірами елементів засновані на надзвичайно широкому колі складних фізико-хімічних процесів: отримання тонких плівок термічним і іонно-плазмовим розпиленням у вакуумі, механічна обробка пластин проводиться за 14-м класом чистоти з відхиленням від площинності не більше 1 мкм, широко застосовується ультразвук і лазерне випромінювання, використовуються відпал у кисні та водні, робочі температури при плавленні металів сягають понад 1500 °C, при цьому дифузійні печі підтримують температуру з точністю 0,5 °C, широко застосовуються небезпечні хімічні елементи та сполуки (наприклад, білий фосфор).

Усе це обумовлює особливі вимоги до виробничої гігієни, так звану «електронну гігієну», адже у робочій зоні обробки напівпровідникових пластин або на операціях складання кристала не повинно бути більше п'яти порошинок розміром 0.5 мкм у 1 л повітря. Тому в чистих кімнатах на фабриках по виробництву подібних виробів усі працівники зобов'язані носити спеціальні, виготовлені з металізованої тканини комбінезони, халати, фартухи, куртки з капюшонами і вмонтованими в них захисними окулярами.[1]. В рекламних матеріалах Intel спецодяг працівників отримав назву bunny suit («костюм кролика»)[2][3].

Техпроцеси більше 100 нм

10 мкм

10 мкм = 10 000 нм — технологічний процес відноситься до рівня напівпровідникових технологій, який був досягнутий приблизно в 1971—1972 роках, провідними напівпровідниковими компаніями[4], такими як Intel.

- Intel 4004 ЦП — 1971 рік;

- Intel 8008 ЦП — 1972 рік.

3 мкм

3 мкм = 3 000 нм — техпроцес, що відповідає рівню технології, досягнутому в 1979 році Intel. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 3 мкм.

- Intel 8085 — 1977, було виготовлено з використанням 3.2 мкм техпроцесу;

- Intel 8086 — 1978, техпроцес 3.2 мкм;

- Intel 8088 — 1979, техпроцес 3.2 мкм[6].

1,5 мкм

1,5 мкм = 1 500 нм — техпроцес, що відповідає рівню технології, досягнутому Intel у 1982 році. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 1,5 мкм.

1 мкм

1 мкм = 1 000 нм — техпроцес відноситься до рівня напівпровідникової технології, який був досягнутий приблизно в 1985 році провідними напівпровідниковими компаніями, такими як Intel і IBM.

0,8 мкм

0,8 мкм = 800 нм — техпроцес, що відповідає рівню технології, досягнутому в кінці 1980-х — початку 1990-х років компаніями Intel і IBM.

0,6 мкм

0,6 мкм = 600 нм — техпроцес, досягнутий виробничими потужностями компаніями Intel і IBM в 1994—1995 роках.

0,35 мкм

350 нм — техпроцес, що відповідає рівню технології, досягнутому в 1997 році провідними компаніями-виробниками мікросхем, такими як Intel, IBM, і TSMC. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 0,35 мкм.

- Intel Pentium MMX (P55)

- Intel Pentium Pro

- Pentium II (Klamath)

- МЦСТ-R150 (2001, 150 МГц)

0,25 мкм

250 нм — техпроцес, що відповідає рівню технології, досягнутому в 1998 році провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 0,25 мкм.

Шарів металу до 6; мінімальна кількість масок — 22.

0,18 мкм

180 нм — техпроцес, що відповідає рівню технології, досягнутому в 1999 році провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 0,180 мкм.

Шарів металу до 6-7; мінімальна кількість масок — 22-24.

- AMD Athlon XP (Palomino)

- Intel Pentium III (Coppermine)

0,13 мкм

130 нм — техпроцес, що відповідає рівню технології, досягнутому в 2000-2001 роках провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 130 нм.

- Intel Pentium III Tualatin

- Intel Celeron Tualatin-256 — жовтень 2001

- Intel Pentium M Banias — березень 2003

- Intel Pentium 4 Northwood — січень 2002

- Intel Celeron Northwood-128 — вересень 2002

- Intel Xeon Prestonia і Gallatin — лютий 2002

- AMD Athlon XP Thoroughbred, Thorton і Barton

- AMD Athlon MP Thoroughbred — серпень 2002

- AMD Athlon XP-M Thoroughbred, Barton і Dublin

- AMD Duron Applebred — серпень 2003

- AMD K7 Sempron Thoroughbred-B, Thorton і Barton — липень 2004

- AMD K8 Sempron Paris — липень 2004

- AMD Athlon 64 Clawhammer і Newcastle — вересень 2003

- AMD Opteron Sledgehammer — червень 2003

- МЦСТ Ельбрус 2000 (1891BM4Я) — липень 2008

- МЦСТ-R500S (1891ВМ3) — 2008, 500 МГц

Техпроцеси менше 100 нм

90 нм (0,09 мкм)

90 нм — техпроцес, що відповідає рівню напівпровідникової технології, який було досягнуту до 2002-2003 років. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 90 нм.

Технологічний процес з проектною нормою 90 нм часто використовується з технологіями напруженого кремнію, мідних з'єднань з меншим опором, ніж у раніше застосовуваного алюмінію, а також новим діелектричним матеріалом з низькою діелектричною проникністю.

- Intel Pentium 4 (Prescott)

- МЦСТ-R1000 (2011, 4 ядра, 1 ГГц)

- AMD Turion 64 X2 (мобільний)

- Ельбрус-S (2010)

65 нм (0,065 мкм)

65 нм — техпроцес, що відповідає рівню технології, досягнутому до 2004 року провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 65-70 нм.

- Intel Pentium 4 (Cedar Mill) — 2006-01-16

- Intel Pentium D 900-series — 2006-01-16

- Intel Celeron D (Cedar Mill cores) — 2006-05-28

- Intel Celeron M

- Intel Core — 2006-01-05

- Intel Core 2 — 2006-07-27

- Intel Core 2 Duo

- Intel Core 2 Quad

- Intel Xeon — 2006-03-14

- AMD Athlon 64 — 2007-02-20

- AMD Phenom X3, X4

- AMD Turion 64 X2 (мобильный)

- AMD Turion 64 X2 Ultra (мобильный)

- STI Cell — PlayStation 3 — 2007-11-17

- Microsoft Xbox 360 «Falcon» CPU — 2007-09

- Microsoft Xbox 360 «Opus» CPU — 2008

- Microsoft Xbox 360 «Jasper» CPU — 2008-10

- Microsoft Xbox 360 «Jasper» GPU — 2008-10

- Sun UltraSPARC T2 — 2007-10

- TI OMAP 3 — 2008-02

- VIA Nano — 2008-05

- Loongson — 2009

- Ельбрус-4С — 2014

50 нм (0,050 мкм)

50 нм — техпроцес, що відповідає рівню технології, досягнутому до 2005 року провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 50 нм.

45 нм (0,045 мкм)

45 нм — техпроцес, що відповідає рівню технології, досягнутому до 2006-2007 років провідними компаніями-виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 45 нм. Для мікроелектронної промисловості став революційним, оскільки це був перший техпроцес, що використовує технологію high-k/metal gate[7][8] (HfSiON/TaN в технології компанії Intel), для заміни фізично себе вичерпавших SiO2/poly-Si.

- Intel Core 2 Duo

- Intel Core 2 Quad

- Intel Core i3, i5, i7

- AMD Phenom II X2, X3, X4, X6

- AMD Athlon II X2, X3, X4

- Fujitsu SPARC64 VIIIfx

- XCGPU (APU від GlobalFoundries, з 2010)

32 нм (0,032 мкм)

32 нм — техпроцес, що відповідає рівню технології, досягнутому до 2009—2010 року провідними компаніями-виробниками мікросхем. Відповідає лінійному вирішенню літографічного обладнання, приблизно рівному 32 нм. Восени 2009 компанія Intel перебувала на етапі переходу до цього нового техпроцесу[9][10][11][12][13]. З початку 2011 почали вироблятися процесори за даним техпроцесом.

- Intel Sandy Bridge

- Intel Saltwell

- AMD Bulldozer

- AMD Piledriver (друге покоління Bulldozer)

- Друге покоління AMD APU: Llano, Trinity, Weatherford, Richland (32 нм)

28 нм (0,028 мкм)

У третьому кварталі 2010 року на нових потужностях розташованої на Тайвані фабрики Fab 12 компанії TSMC повинен початися серійний випуск продукції за 28-нанометровою технологією[14].

- Багатоядерні процесори Snapdragon фірми Qualcomm.

- Мобільні процесори Apple A7, виготовлені Samsung.

У травні 2011 за технологією 28 нм фірмою Altera була випущена найбільша у світі мікросхема, що складається з 3,9 млрд транзисторів[15].

22 нм (0,022 мкм)

22 нм — техпроцес, що відповідає рівню технології, досягнутому до 2009—2012 роках провідними компаніями — виробниками мікросхем. Відповідає лінійній роздільній здатності літографічного обладнання, приблизно рівній 22 нм. 22-нм елементи формуються при літографії шляхом експонування маски світлом довжиною хвилі 193 нм[20][21].

У 2008 році, на щорічній виставці високих технологій International Electron Devices Meeting у Сан-Франциско технологічний альянс компаній IBM, AMD і Toshiba продемонстрував комірку пам'яті SRAM, виконану за 22-нм техпроцесом з транзисторів типу FinFET, які, у свою чергу, виконуються за прогресивною технологією high-k/metal gate (затвори транзистора виготовляються не з кремнію, а з гафнію), площею всього 0,128 мкм ² (0,58 × 0,22 мкм)[22]. Також про розробку комірки пам'яті типу SRAM площею 0,1 мкм ² створену по техпроцесу 22 нм оголосили IBM і AMD[23]. Перші працездатні тестові зразки регулярних структур (SRAM) представлені публіці компанією Intel в 2009 році[24]. 22-нм тестові мікросхеми являють собою пам'ять SRAM і логічні модулі. SRAM-осередки розміром 0,108 і 0,092 мкм² функціонують у складі масивів за 364 млн біт. Осередок площею 0,108 мкм² оптимізований для роботи в низьковольтному середовищі, а осередок площею 0,092 мкм² є найбільш мініатюрним з відомих сьогодні осередків SRAM.

Виробляються процесори за такою технологією з початку 2012 року.

- Intel Ivy Bridge / Ivy Bridge-E

- Intel Haswell (послідовник Ivy Bridge, із вбудованим GPU).

- Intel Bay Trail-M (мобільні Pentium і Celeron на мікроархітектурі Silvermont; вересень 2013)

16 нм FinFET

Станом на вересень 2014 TSMC продовжує розробки 16 нм техпроцесу на транзисторах з вертикально розташованим затвором (fin field effect transistor, FinFET) і планує почати 16 нм виробництво в 1 кварталі 2015 року[25].

14 нм (0,014 мкм)

Будівництво заводу під назвою Fab42 в американському штаті Аризона почалося в середині 2011 року, а в експлуатацію він буде зданий в 2013 році. За заявою Intel, він стане найсучаснішим заводом з масового випуску комп'ютерних процесорів — Intel буде випускати тут продукцію по 14-нанометровій технології на основі 300-міліметрових кремнієвих пластин. Завод також стане першим масовим виробництвом, сумісним з 450-мм пластинами[26][27]. У будівництво планується вкласти понад $ 5 млрд. На момент запуску Fab 42 стане, як очікується, одним з найбільш передових у світі заводів з випуску напівпровідникової продукції у великих обсягах.

У січні 2014 року Intel оголосила про затримку відкриття заводу Fab 42[28]. Відкриття заводу планується у IV кварталі 2014 року, масове виробництво в I кварталі 2015 року[29].

Станом на травень 2014 компанія Samsung продовжує розробки техпроцесів 14 нм LPE/LPP[30]. У 2015 році Samsung випускатиме процесори для Apple за нормами 14 нм[31].

10 нм (0,01 мкм)

Тайванський напівпровідниковий виробник United Microelectronics (UMC) повідомив, що приєднається до технологічного альянсу IBM для участі в розробці 10-нм CMOS-техпроцесу[32].

У 2011 році публікувалася інформація про плани Intel щодо випуску серверних рішень і розвитку техпроцесу 10 нм до 2018 року[33].

Пробний випуск продукції компанії Taiwan Semiconductor Manufacturing Company (TSMC) за нормами 10 нм намічений на 2015 рік, а серійний — на 2016 рік[34].

У телефоні Samsung Galaxy S8 2017 року використовується 10-нанометровий техпроцес.

7 нм (0,007 мкм)

За деякими даними Intel планує вийти на ринок з технологічним процесом 7 нм у 2017 році[35].

6 нм (0,006 мкм)

16 квітня 2019 р. компанія TSMC анонсувала освоєння технологічного процесу 6-нм в ризиковому виробництві, що дозволяє збільшити щільність елементів мікросхем на 18 %. Цей техпроцес є більш дешевою альтернативою техпроцесу 5 нм, він дозволяє легко масштабувати топології, розроблені для 7 нм.[36]

5 нм (0,005 мкм)

В першій половині 2019 року компанія TSMC розпочала ризикове виробництво чипів за 5-нм техпроцесом.[37] Перехід на цю технологію дозволяє збільшити щільність електронних компонентів на 80 % і підвищити швидкодію на 15 %[38] .

Технологічний процес 5 нм кінцеві користувачі отримали у 2020 році, зокрема на його основі виготовлений процесор Aplle A14 Bionic. На думку деяких експертів, 5 нм буде кінцем закону Мура[39].

Менше 5 нм

Відповідно до закону Мура, взявши за точку відліку очікувану в 2020-му році появу 5 нм техпроцесу, можна спрогнозувати, що технологія 4 нм з'явиться приблизно в 2022, 3 нм у 2024 році, 2 нм у 2026 році, й, нарешті, 1 нм у 2028 році, який може стати межею для поточних літографічних технологій напівпровідникового кремнію у його нинішній реалізації[40]. У результаті у 2030 і наступних роках можна бути побачити зрушення у технології, що дадуть більш дрібні компоненти у вигляді силіцію або кремнієвих нанотрубок.

Див. також

Примітки

- Городилин Ст. М., Городилин Ст. Ст.. § 21. Випромінювання, їх дії на навколишнє середовище та заходи боротьби за екологію. // Регулювання радіоапаратури. — Видання четверте, виправлене і доповнене. — М. : Вища школа, 1992. — С. 79. — ISBN 5-06-000881-9.

- Мініатюрність, чистота. Архів оригіналу за 5 серпня 2013. Процитовано 11 січня 2015.

- Intel Museum — From Sand to Circuits

- Mueller, S (21 липня 2006). Microprocessors from 1971 to the Present. informIT. Процитовано 11 травня 2012.

- Архівована копія. Архів оригіналу за 14 лютого 2012. Процитовано 10 січня 2015.

- http://www.listoid.com/list/142

- PRESS KIT — First 45nm Chips: Eco-Friendly. Faster. ‘Cooler’.

- Intel Demonstrates High-k + Metal Gate Transistor Breakthrough on 45 nm Microprocessors

- Intel 32nm Logic Technology(англ.)

- процессоры Intel по 32-нм технологии. Архів оригіналу за 30 березня 2010. Процитовано 17 січня 2015.

- New Details on Intel's Upcoming 32nm Logic Technology(англ.)

- White Paper Introduction to Intel's 32nm Process Technology(англ.)

- High Performance 32nm Logic Technology Featuring 2nd Generation High-k + Metal Gate Transistors

- TSMC подолала складності 40-нанометрової технології і в цьому році почне випуск за нормами 28 нм. Архів оригіналу за 6 жовтня 2017. Процитовано 8 травня 2019.

- Корпорація Altera встановила новий галузевий рекорд - Програмована вентильна матриця (FPGA) Stratix V. Архів оригіналу за 5 березня 2016. Процитовано 10 січня 2015.

- AMD виправляє мінуси в архітектурі Bulldozer Steamroller

- Нова архітектура AMD «Steamroller» у 2014? // 3.01.2013

- МЦСТ. = Новий 8-ядерний мікропроцесор Ельбрус-8С.[недоступне посилання з липня 2019]

- Восьмиядерний мікропроцесор з архітектурою Ельбрус. Архів оригіналу за 25 червня 2014. Процитовано 10 січня 2015.

- Новини з форуму Intel, який проходив з 22 по 24 вересня у Сан-Франциско для розробників (Intel Developer Forum, IDF)[недоступне посилання з липня 2019]

- Розетський камінь літографії, 2013-11-20, за матеріалами Lars Leibmann, The Escalating Design Impact of Resolution-Challenged Lithography. ICCAD 2013

- IBM, AMD і Toshiba продемонстрували першу 22-нм комірку пам'яті SRAM[недоступне посилання з травня 2019]

- IBM і AMD продемонструють 22 нм комірку пам'яті. Архів оригіналу за 5 березня 2016. Процитовано 10 січня 2015.

- Intel Developer Forum 22nm News Facts

- TSMC почне 16 нм виробництво в 1 кварталі 2015 року.

- A First Look at Intel's 14nm Fab 42 Manufacturing Facility // January 25, 2012 by Douglas Perry — source: VLSI Research; російською: Intel Fab 42: первые фото строящегося производства по созданию 14 нм процессоров. Цитата: «first volume production facility that is compatible with 450 mm wafers»

- Update: Intel to build fab for 14-nm chips // Mark LaPedus 2/18/2011 «Fab 42, will be a 300-mm plant. It will also be compatible for 450-mm»

- to worry-about Intel cancels 14nm Fab 42 in Arizona, due to increasing competition from ARM. // ExtremeTech

- Intel postpones Broadwell to availability 4Q14

- http://www.digitimes.com/news/a20140514PD208.html

- Samsung випускатиме процесори для Apple за нормами 14 нм. Архівовано 5 липня 2017 у Wayback Machine. // iXBT.com

- UMC приєднається до IBM у розробці 10-нм техпроцесу

- Слайд Intel вказує на 10-нм техпроцес у 2018 році

- У майбутньому році TSMC планує почати пробний, а в 2016 році - серійний випуск продукції за нормами 10 нм. Архів оригіналу за 10 лютого 2019. Процитовано 8 травня 2019.

- IDF 2013: Intel Shows Plans For 7 nm Chips; 22 nm LTE Atoms are Shipping. DailyTech. 11 вересня 2013. Архів оригіналу за 3 січня 2015. Процитовано 10 січня 2015.

- TSMC Unveils 6-nanometer Process (англ.). TSMC. Процитовано 18 квітня 2019.

- TSMC завершила разработку 5-нм техпроцесса — началось рисковое производство (рос.). 3DNews - Daily Digital Digest. Процитовано 10 квітня 2019.

- TSMC and OIP Ecosystem Partners Deliver Industry’s First Complete Design Infrastructure for 5nm Process Technology (англ.). TSMC. Процитовано 18 квітня 2019.

- End of Moore's Law: It's not just about physics. CNET. 28 серпня 2013.

- Samsung's Kim Claims No Limit to Scaling