Модуль керування пам'яттю

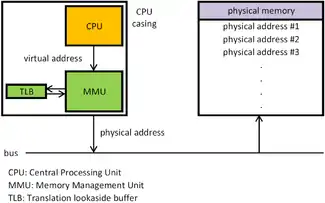

Модуль керування пам'яттю (МКП), іноді званий модулем керування сторінковою пам'яттю (МКСП), — комп'ютерний апаратний модуль, що має всі посилання на пам'ять, які проходять через нього, насамперед перекладаючи віртуальні адреси пам'яті у фізичні. Він зазвичай реалізований як частина центрального процесора (ЦП), але також може бути у вигляді окремої мікросхеми.

МКП ефективно виконує керування віртуальною пам'яттю, одночасно оброблюючи захист пам'яті, контроль кешу, арбітраж шин і, у простіших комп'ютерних архітектурах (особливо 8-бітних системах), перемикання банків.

Огляд

Сучасні MMU зазвичай ділять віртуальний адресний простір (діапазон адрес, використовуваних процесором) на сторінки, розмір кожної з яких є степенем 2, зазвичай кілька кілобайтів, але вони можуть бути значно більшими. Нижні біти адреси (зміщення всередині сторінки) залишаються незміненими. Верхні біти адреси є номерами віртуальних сторінок[2].

Записи таблиці сторінок

Більшість МКП використовують таблиці елементів у пам'яті, звані «таблицями сторінок», що містить один «запис таблиці сторінок» (ЗТС) на сторінку, для відображення віртуальних номерів сторінок у фізичні в основній пам'яті. Асоціативний кеш ЗТС називається буфером асоціативної трансляції (БАТ) та використовується для уникнення необхідності доступу до основної пам'яті при кожному відображенні віртуальної адреси. Інші МКП можуть мати приватний масив пам'яті[3] чи регістри, що містять набір записів таблиці сторінок. Фізичні номери сторінок об'єднуються зі зміщеннями сторінок і дають повну фізичну адресу.

ЗТС також може включати інформацію про те, чи була сторінка записана («біт забрудненості»), коли її було востаннє використано («біт доступу», для за найменш нещодавно використаними (LRU) задачі заміщення сторінок), який вид процесів (користувацького чи режиму супервізора) можуть читати та писати її, і чи повинна вона кешуватися.

Іноді ЗТС забороняє доступ до віртуальної сторінки, можливо, через відсутність фізичної пам'яті з довільним доступом, виділеної цій сторінці. У цьому випадку МКП сигналізує ЦП про відмову сторінки. Потім операційна система (ОС) обробляє ситуацію, можливо, намаганням знайти вільну сторінку RAM і встановити новий ЗТС для відображення цієї сторінки на запитувану віртуальну адресу. За відсутності вільної RAM може бути необхідним обрати деяку сторінку (відому як «жертва») з використанням деякого алгоритму заміни та зберегти її на диск (цей процес називається «підкачуванням»). З деякими МКП також можлива нестача ЗТС, у цьому випадку ОС матиме звільнити його для нового відображення.

МКП також можуть генерувати стани помилки незаконного доступу чи відмови недійсної сторінки за незаконного доступу чи доступу до неіснуючої пам'яті відповідно, що призводить до помилки сегментації чи помилки шини під час обробки операційною системою.

Переваги

У деяких випадках відмова сторінки може позначати баг, якому можна запобігти шляхом використання захисту пам'яті як однієї з ключових переваг МКП: операційна система може його використати для захисту від помилкових програм шляхом заборони доступу до пам'яті, до якої конкретна програма не повинна мати доступ. Зазвичай операційна система призначає кожній програмі власний віртуальний адресний простір.

МКП також пом'якшує проблему фрагментації пам'яті. Після виділення та звільнення блоків пам'яті вільна пам'ять може стати фрагментованою (розривною) так, що найбільший послідовний блок вільної пам'яті може бути набагато меншим за загальний обсяг. Із віртуальною пам'яттю сусідній діапазон віртуальних адрес може відображатися на декілька непослідовних блоків фізичної пам'яті; це непослідовне виділення є однією з переваг підкачки.

У деяких ранніх конструкціях мікропроцесорів керування пам'яттю здійснювалося окремою мікросхемою, як-от схеми надвеликого рівня інтеґрації VI475 (1986), Motorola 68851 (1984, для використання разом з процесором Motorola 68020), або Z8015 (1985)[4], що використовується в родині процесорів Zilog Z8000. Пізніші мікропроцесори (як-от Motorola 68030, Zilog Z280 і Intel 80386) розміщували MMU на одному кристалі з процесором.

Тоді як дана стаття зосереджується на сучасних МКП, зазвичай на основі сторінок, ранні системи використовували аналогічну концепцію для адресації з базовою межею, що в подальшому було розвинуто до сегментації. Вони іноді також присутні в сучасних архітектурах. Архітектура x86 забезпечує сегментацію, але не підкачку, в 80286, і забезпечує підкачку та сегментацію в 80386 і пізніших процесорах (хоча використання сегментації недоступне в 64-бітних операціях).

Приклади

Більшість сучасних систем ділять пам'ять на сторінки розміром 4-64 кБ, часто зі здатністю використовувати величезні сторінки розміром від 2 МБ до 1 ГБ. Переклади сторінок кешуються у буфері асоціативної трансляції (БАТ). Деякі системи, переважно старіших RISC конструкцій, ловлять у ОС, коли переклад сторінки не знайдено в БАТ. Більшість систем використовують апаратний обхідник дерев. Більшість систем дозволяють МКП вимикатися, але деякі вимикають МКП, потрапляючи до коду ОС.

VAX

VAX сторінки сягають 512 байтів, що дуже мало. ОС може розглядати їх так, якби вони були єдиною більшою сторінкою. Наприклад, Linux на VAX групує разом вісім сторінок. Таким чином, система розглядається такою, що має 4 кБ сторінки. VAX ділить пам'ять на чотири ділянки з фіксованим призначенням розміром 1 ГБ кожна. Це:

- Простір P0

- Використовується для пам'яті загального призначення для кожного процесу, як-от купи.

- Простір P1

- (контрольний простір) також для кожного процесу та зазвичай використовується для супервізора, виконавчих, ядра та користувацьких стеків, а також інших контрольних структур для кожного процесу, керованих операційною системою.

- Простір S0

- (системний простір) глобальний для всіх процесів і зберігає код і дані операційної системи, підкачені чи ні, включно з таблицями сторінок.

- Простір S1

- Не використовується та «зарезервований для Digital».

Таблиці сторінок є великими лінійними масивами. Як правило, це дуже марнотратно, коли адреси використовуються на обох кінцях можливого діапазону, але сама таблиця сторінок для застосунків зберігається в підкаченій пам'яті ядра. Таким чином, ефективне дворівневе дерево дозволяє застосункам мати запасний розподіл пам'яті, не витрачаючи багато місця на невикористані записи таблиць сторінок. МКП VAX відрізняються відсутністю доступного біту. ОС, які реалізують підкачку, повинні знайти деякий спосіб емуляції доступного біту, якщо вони хочуть ефективно працювати. Зазвичай ОС періодично скасовує відображення сторінок так, що відмови неіснуючої сторінки можуть використовуватися, аби дати ОС встановити доступний біт.

ARM

Прикладні процесори на основі архітектури ARM реалізують МКП, визначені системною архітектурою віртуальної пам'яті ARM. Поточна архітектура визначає ЗТС для опису 4 кБ і 64 кБ сторінок, 1 МБ розділів і 16 МБ надрозділів; успадковані версії також визначають 1 кБ крихітні сторінки. ARM використовує дворівневу таблицю сторінок при використанні 4 кБ і 64 кБ сторінок, або просто однорівневими таблицями сторінок для 1 МБ розділів і 16 МБ розділів.

Оновлення БАТ виконуються автоматично апаратним забезпеченням обходу таблиці сторінок. ЗТС включають дозвіл доступу на читання та запис на основі привілеїв, кешування інформації, NX bitу та незахищеного біту[5].

IBM System/360 Model 67, IBM System/370 і наступники

Мейнфрейм IBM System/360 Model 67, представлений серпні 1965 року, мав окрему схему керування сторніками пам'яті, що називалася англ. DAT box (Dynamic Address Translation)[6][7]. DAT box мав досить незвичайну можливість зберігання бітів сторінки «було звернення» (англ. accessed) та «брудна» (англ. dirty) поза таблицею сторінок. Вони[хто?] посилаються на фізичну пам'ять, а не на віртуальну, і доступ до них надається інструкціями спеціального призначення. Це зменшує накладні витрати для ОС, яка інакше мала б поширювати біти accessed і dirty з таблиць сторінок до більш фізично-орієнтованої структури даних. Це спрощує віртуалізацію на рівні ОС[прояснити].

Починаючи з серпня 1972 року IBM System/370 має схожий МКП, хоча він спочатку підтримував лише 24-бітний віртуальний адресний простір, а не 32-бітний із System/360 Model 67. Він також зберігав біти «було звернення» та «брудна» поза таблицею сторінок. На початку 1983 року архітектура System/370-XA розширила віртуальний адресний простір до 31 біту, а 2000 року було представлено 64-бітну z/Architecture з розширеним адресним простором до 64 бітів; вона продовжила зберігати біти статусу сторінки (accessed і dirty) поза таблицею сторінок.

DEC Alpha

Процесор DEC Alpha ділить пам'ять на 8 кБ сторінки. Після промаху БАТ низькорівневий вбудований машинний код (тут названий PALcode) обходить трирівневу деревоподібну таблицю сторінок. Адресація розбита наступним чином: 21 біт не використовується, по 10 бітів індексують кореневий, середній і рівень листя дерева, а 13 бітів проходять до фізичної адреси без модифікацій. Підтримуються повні біти дозволу на читання, запис і виконання.

MIPS

Архітектура MIPS підтримує до 64 записів у БАТ. Кількість записів БАТ налаштовується у конфігурації ЦП до синтезу. Записи БАТ подвійні. Кожен запис БАТ відображає номер віртуальної сторінки (НВС2) на один із двох номерів кадру сторінок (НКС0 чи НКС1) залежно від останнього значущого біту віртуальної адреси, що не є частиною маски сторінки. Цей біт і біти маски сторінки не зберігаються у НВС2. кожен запис БАТ має власний розмір сторінки, який може бути будь-яким значенням від 1 кБ до 256 МБ, кратним чотирьом. Кожен НКС у записі БАТ має атрибут кешування, брудний і дійсний біт стану. НВС2 має глобальний біт стану й ID, який призначається ОС і бере участь у зіставленні запису БАТ віртуальних адрес, якщо глобальний біт стану встановлений у нуль. НКС зберігає фізичну адресу без бітів маски сторінки.

Виняток перенаповнення БАТ генерується, коли жоден запис у БАТ не збігається з відображеною віртуальною адресою. Виняток недійсного БАТ генерується, коли є збіг, але запис позначено недійсним. Виняток модифікованого БАТ генерується, коли є збіг, але брудний стан не встановлено. Якщо виняток БАТ стається під час обробки винятку БАТ, тобто виняток подвійної помилки БАТ відправляється до власного обробника винятків.

MIPS32 і MIPS32r2 підтримують 32 біти віртуального та до 36 бітів фізичного адресного простору. MIPS64 підтримує до 64 бітів віртуального та до 59 бітів фізичного адресного простору.

Sun 1

Оригінальний Sun 1, представлений 1982 року, є одноплатним комп'ютером, побудованим навколо мікропроцесора Motorola 68000. Він містить оригінальний модуль керування пам'яттю Sun-1, що забезпечує трансляцію адрес, захист, спільне використання та виділення пам'яті для багатьох процесів, які працюють у ЦП. Весь доступ ЦП до приватної вбудованої RAM, зовнішньої пам'яті Multibus, вбудованого та Multibus введення-виведення відбувається через МКП, де він транслюється та захищається єдиним способом. МКП реалізовано в апаратному забезпеченні на платі ЦП.

МКП складається з контекстного регістру та карт сегментів і сторінок. Віртуальні адреси з ЦП транслюються у проміжні картою сегментів, які, у свою чергу, транслюються у фізичні адреси картою сторінок. Розмір сторінки дорівнює 2 кБ, а сегменту — 32 кБ, що дає 16 сторінок у сегменті. До 16 контекстів можуть відображатися одночасно. Максимум простору логічних адрес для контексту дорівнює 1024 сторінкам або 2 МБ. Максимум фізичних адрес, які можуть одночасно відображатися, також дорівнює 2 МБ.

Контекстний регістр важливий у багатозадачній операційній системі, оскільки він дозволяє ЦП перемикатися між процесами без перезавантаження всієї інформації про стан трансляції. 4-бітний контекстний регістр може перемикатися між 16 розділами карти сегментів під керуванням супервізора, який дозволяє 16 контекстам одночасно відображатися. Кожен контекст має власний віртуальний адресний простір. Спільне використання віртуального адресного простору та міжконтекстне спілкування може забезпечуватися записом однакових значень у карти сегментів або сторінок різних контекстів. Додаткові контексти можуть оброблятися, розглядаючи карту сегментів як контекстний кеш і замінюючи застарілі контексти на основі найменш нещодавнього використання.

Контекстний регістр не розрізняє стани користувача та супервізора. Переривання та пастки не перемикають контексти, що вимагає завжди відображати всі дійсні вектори переривання у сторінку 0 контексту, як і валідний стек супервізора[8].

PowerPC

У PowerPC G1, G2, G3 і G4 сторінки зазвичай 4 кБ. Після промаху БАТ стандартний МКП PowerPC починає два одночасні пошуки. Один пошук намагається зіставити адресу з одним із чотирьох чи восьми регістрів трансляції адрес блоків даних (ТАБД) або інструкцій (ТАБІ) за необхідності. Регістри ТБА можуть відображати лінійні шматки пам'яті завбільшки 256 МБ, і зазвичай використовуються ОС для відображення великих порцій адресного простору для власного використання ядром ОС. У разі успішного пошуку ТБА інший пошук зупиняється й ігнорується.

Інший пошук, непрямо підтримуваний всіма процесорами цієї родини, здійснюється через так звану «інвертовану таблицю сторінок», яка діє як хешоване розширення БАТ поза чипом. Спочатку верхні чотири біти адреси використовуються для вибору одного з 16 сегментних регістрів. Потім 24 біти з сегментного регістру замінюють ті чотири біти, виробляючи 52-бітну адресу. Використання сегментних регістрів дозволяє багатьом процесам спільно використовувати ту саму геш-таблицю.

52-бітна адреса хешується, а потім використовується як індекс таблиці поза чипом. Там група восьмисторінкових табличних записів сканується на один зі збігів. За відсутності збігу через надмірні колізії гешу процесор повторює спробу з дещо іншою хеш-функцією. Якщо це також не вдається, то ЦП потрапляє до пастки в ОС (з вимкненим МКП) так, що проблему може бути вирішено. ОС має відкинути запис із геш-таблиці для звільнення простору для нового запису. ОС може генерувати новий запис із нормальнішої деревоподібної таблиці сторінок або зі структур даних на відображення, які, ймовірно, будуть повільнішими й ефективнішими за простором. Підтримка невиконуваного керування наявна в сегментних регістрах, що призводить до зернистості 256 МБ.

Основною проблемою цієї конструкції є погане місцерозташування кешу, спричинене хеш-функцією. Деревоподібні конструкції уникають цього, розміщуючи записи таблиці сторінок для суміжних сторінок у суміжних місцях. Операційна система, що працює на PowerPC, може мінімізувати розмір хеш-таблиці для зменшення цієї проблеми.

Також дещо повільне вилучення записів таблиць сторінок процесу. ОС може уникнути повторного використання сегментних значень, аби затримати появу цього, чи вона може пожертвувати пам'яттю, асоційованою з хеш-таблицями на процес. Чипи G1 не шукають записи таблиці сторінок, але можуть генерувати хеш із очікуванням того, що ОС програмно шукатиме стандартну хеш-таблицю. ОС може писати до БАТ. Чипи G2, G3 і ранні G4 апаратно шукають хеш-таблицю. Останні чипи дозволяють ОС будь-який метод. На чипах, які роблять його необов'язковим або не підтримують узагалі, ОС може ексклюзивно вибрати використання деревоподібної таблиці сторінок.

IA-32 / x86

Архітектура x86 розвивалася протягом дуже довгого часу, підтримуючи повну програмну сумісність, навіть для коду ОС. Таким чином, МКП надзвичайно складні, з багатьма різними можливими операційними режимами. Тут описані нормальні операції традиційного ЦП 80386 та його наступників (IA-32).

ЦП насамперед ділить пам'ять на 4 кБ сторінки. Сегментні регістри, фундаментальні для старіших конструкцій МКП 8088 і 80286, не використовуються в сучасних ОС за одним основним винятком: доступу до даних конкретного потоку для застосунків або даних конкретного ЦП для ядер ОС, які виконуються з явним використанням сегментних регістрів FS і GS. Увесь доступ до пам'яті залучає сегментний регістр, вибраний відповідно до виконуваного коду. Сегментний регістр діє як індекс у таблиці, що надає зміщення для додавання до віртуальної адреси. За винятком використання FS або GS, ОС забезпечує, що зміщення дорівнюватиме нулю.

Після додавання зміщення адреса маскується, аби не перевищувати 32 біти. Результат можна подивитися через деревоподібну таблицю сторінок, де біти адреси будуть розділені наступним чином: по 10 бітів для гілки дерева та листя гілки, а 12 найнижчих бітів прямо скопійовані до результату. Деякі операційні системи, як-от OpenBSD зі своєю особливістю W^X і Linux із виправленнями Exec Shield або PaX, також можуть обмежувати довжину сегменту коду, як зазначено в регістрі CS, для заборони виконання коду у змінних ділянках адресного простору.

Незначні зміни МКП, введені з Pentium, дозволили дуже великі 4 МБ сторінки пропуском нижнього рівня дерева (це залишає 10 бітів для індексування першого рівня ієрархії сторінок, а решта 10+12 бітів прямо копіюється до результату). Незначні зміни МКП, введені з Pentium Pro, ввели можливість розширення фізичних адрес (РФА), дозволяючи 36-бітним фізичним адресам із 2+9+9 бітами для трирівневих таблиць сторінок і 12 найнижчими бітами, що прямо копіюються до результату. Великі сторінки (2 МБ) також доступні пропуском нижнього рівня дерева (маючи наслідком 2+9 бітів для дворівневої ієрархії таблиць і решту 9+12 найнижчих бітів, що копіюються прямо). На додачу, таблиця атрибутів сторінок дозволила специфікацію кешування шляхом пошуку кількох вищих бітів у малій таблиці всередині ЦП.

Підтримка невиконання спочатку забезпечувалася лише на сегментній основі, чим було дуже незручно користуватися. Пізніші чипи x86 забезпечили сторінкові біти невиконання в режимі РФА. Вищеописані механізми W^X, Exec Shield і PaX емулюють сторінкову підтримку невиконання на машинах із процесорами x86 без біту NX встановленням довжини сегменту коду зі втратами продуктивності та зменшенні доступного адресного простору.

x86-64

x86-64 — 64-бітне розширення x86, що майже цілком вилучає сегментацію на користь пласкої моделі пам'яті, що використовується майже всіма операційними системами для 386 чи новіших процесорів. У довгому режимі всі сегментні зміщення ігноруються, за винятком сегментів FS і GS. При використанні зі сторінками 4 кБ дерево таблиці сторінок має чотири рівні замість трьох.

Віртуальні адреси діляться наступним чином: 16 бітів не використовуються, по дев'ять бітів для чотирьох рівнів дерева (загалом 36 бітів), а 12 найнижчих бітів прямо копіюються до результату. З 2 МБ сторінками наявні лише три рівні таблиці сторінок, де загалом 27 бітів використовуються у підкачці та 21 біт у зміщенні. Деякі новіші ЦП також підтримують 1 ГБ сторінку з двома рівнями підкачки та 30 bits зміщення[9].

CPUID може використовуватися для визначення підтримки 1 ГБ сторінок. В усіх трьох випадках вимагається рівність 16 highest бітів 48-му біту, чи, іншими словами, нижчі 48 бітів є знаковим розширенням вищих бітів. Це робиться, аби дозволити майбутнє розширення адресного діапазону без загрози зворотній сумісності. В усіх рівнях таблиці сторінок її записи включають біт невиконання.

Unisys MCP Systems (Burroughs B5000)

Burroughs B5000 1961 року є першою комерційною системою з підтримкою віртуальної пам'яті (після Atlas), навіть хоча вона не має МКП[10]. Вона забезпечує дві функції МКП — адресування віртуальної пам'яті та захист пам'яті — з різними архітектурними підходами.

Перший, у відображенні віртуальних адрес пам'яті, замість потреби у МКП системи MCP засновані на дескрипторах. Кожен виділений блок пам'яті отримує головний дескриптор зі властивостями блоку (тобто розмір, адреса та наявність у пам'яті). При отриманні запиту до блоку на читання чи запис апаратне забезпечення перевіряє його наявність через біт наявності (нбіт) в дескрипторі.

Значення 1 нбіту позначає наявність блоку. У цьому випадку до блоку можна отримати доступ через фізичну адресу в дескрипторі. Якщо нбіт дорівнює нулю, генерується переривання для MCP (операційної системи), аби зробити блок наявним. Якщо адресне поле дорівнює нулю, то це перший доступ до блоку й він виділяється (початковий нбіт). Якщо ж адресне поле ненульове, то це дискова адреса блоку, який раніше було викинуто, тому блок завантажується з диску, нбіт встановлюється в одиницю, а фізична адреса пам'яті оновлюється для вказування на блок у пам'яті (інший нбіт). Це робить дескриптори еквівалентами записам таблиці сторінок у системі МКП. Продуктивність системи можна контролювати через кількість нбітів. Початкові нбіти позначають початкові нбіти, але вищий рівень інших нбітів позначають, що система може побитися.

Тому всі виділення пам'яті повністю автоматичні (одна з особливостей сучасних систем[11]) і немає способу виділити блоки інакше, ніж цим механізмом. Немає таких викликів, як malloc або dealloc, оскільки блоки пам'яті також автоматично відкидаються. Схема також ледача, оскільки блок не виділятиметься, доки на нього дійсно не буде посилання. Коли пам'ять майже повна, MCP обстежує робочий набір, намагаючись ущільнити (оскільки система сегментована, а не сторінкована), звільняючи сегменти лише для читання (як-от сегменти коду, які можуть відновлюватися з їх оригінальної копії) та, як останній засіб, скидаючи брудні сегменти даних на диск.

Інший спосіб, яким B5000 забезпечує функцію МКП, полягає в захисті. Оскільки весь доступ здійснюється через дескриптор, апаратне забезпечення може перевірити, що всі доступи в допустимих межах і, в разі запису, що процес має дозвіл на запис. Система MCP по суті безпечна, а тому не вимагає МКП для забезпечення цього рівня захисту пам'яті. Дескриптори є лише для читання для користувацьких процесів і можуть оновлюватися лише системою (апаратним забезпеченням або MCP) (слова, тег яких є непарним числом, є тільки для читання; дескриптори мають тег 5, а слова коду — 3).

Блоки можуть спільно використовуватися процесами через копіювання дескрипторів у стек процесу. Таким чином, деякі процеси можуть мати дозвіл на запис, тоді як інші — ні. Сегмент коду є тільки для читання, а тому відновлюється та спільно використовується процесами. Копії дескрипторів містять 20-бітне адресне поле, що дає індекс головного дескриптора в їх масиві. Це також реалізує дуже ефективний і безпечний механізм IPC. Блоки легко можуть перерозподілятися, оскільки лише головний дескриптор потребує оновлення при зміні стану блоку.

Єдиним іншим аспектом є продуктивність: чи забезпечують системи на основі чи не на основі МКП кращу продуктивність? Системи MCP можуть реалізовуватися нагорі стандартного апаратного забезпечення, що має МКП (наприклад, стандартний ПК). Навіть, якщо реалізація системи так чи інакше використовує МКП, це не буде видимим узагалі на рівні MCP.

Див. також

- Керування пам'яттю

- Контролер пам'яті

- Сегментація пам'яті

Примітки

- Tanenbaum, Andrew S. (2009). Modern operating systems. Upper Saddle River (Нью-Джерсі): Prentice-Hall. ISBN 0-13-600663-9.

- Uyeda, Frank (2009). Lecture 7: Memory Management (PDF). CSE 120: Principles of Operating Systems. UC San Diego. Процитовано 4 грудня 2013.

- Spectra 70 70-46 Processor Manual. RCA. березень 1968. с. 4. Процитовано 15 серпня 2013.

- Electronic Datasheet Search And Download Site (PDF). Ic-on-line.cn. Процитовано 3 травня 2017.[недоступне посилання з червня 2019]

- Cortex-A8 Technical Reference Manual (PDF). Infoventer.arm.com. Процитовано 3 травня 2017.

- IBM Archives: System/360 Dates and characteristics. 03.ibm.com. Процитовано 3 травня 2017.

- IBM System/360 Model 67 Functional Characteristics (PDF) (вид. 3). лютий 1972. GA27-2719-2.

- Sun 68000 Board User's Manual (вид. Revision B). Sun Microsystems. лютий 1983.

- AMD64 Architecture Programmer's Manual Volume 2: System Programming (PDF). support.amd.com. березень 2017. Процитовано 5 грудня 2017.

- Tanenbaum, Andrew S.; Herder, Jorrit N.; Bos, Herbert (травень 2006). Can We Make Operating Systems Reliable and Secure?. Computer 39 (5): 44—51. doi:10.1109/MC.2006.156.

- Ingalls, Daniel H. H. (серпень 1981). Архівована копія. Byte Magazine. Архів оригіналу за 27 вересня 2007. Процитовано 16 грудня 2018. Вказано більш, ніж один

|назва=та|title=(довідка); Вказано більш, ніж один|url-архіву=та|archiveurl=(довідка); Вказано більш, ніж один|дата-архіву=та|archivedate=(довідка); Вказано більш, ніж один|мертвий-url=та|deadurl=(довідка)

Дану статтю засновано на матеріалах, узятих із «Free On-line Dictionary of Computing» до 1 листопада 2008 року та «переліцензовано» на умовах GFDL версії 1.3 чи пізнішої.