Icarus Verilog

Icarus Verilog — компілятор мови опису апаратури Verilog, призначений для симуляції та веріфікації. Програма має можливість підключення модулів розширення симуляції та кодогенерації[3].

| |

| Автор(и) | Stephen Williams |

|---|---|

| Стабільний випуск | 10.0 [1] (23 серпня 2015) |

| Версії | 11.0 (11 жовтня 2020)[2] |

| Репозиторій | github.com/steveicarus/iverilog |

| Нестабільний випуск | 10.1.1 (10 лютого 2016) |

| Платформа | Крос-платформна |

| Операційна система | Linux, Windows, FreeBSD, Mac OS X, OpenSolaris |

| Мова програмування | C++ |

| Ліцензія | GPL, MIT |

| Вебсайт | iverilog.icarus.com |

Симуляція виконується віртуальною машиною. Результати симуляції записуються у стандартному форматі VCD (англ. Value Change Dump — дамп зміни значень), для перегляду результатів симуляції у вигляді графіків сигналів необхідна відповідна програма, наприклад, GTKWave.

Програма є вільною й розповсюджується під ліцензією GPL, частина файлів коду програми має ліцензію MIT[4]

Icarus Verilog працює в операційних системах GNU/Linux, Windows, FreeBSD, Mac OS X та OpenSolaris.

Історія

Автором програми є Стефан Вільямс (англ. Stephen Williams), який почав працювати над програмою в 1998 році. У інтерв'ю журналу Linux Journal він відповів на запитання щодо віку проекту[5]:

LinuxJournal: Як довго Ви працюєте над Icarus Verilog? Stephen Williams: Мої логи показують, що його було внесено в CVS в листопаді 1998 року. У мене було кілька невдалих спроб, принаймні два роки до цього. Якщо не зраджує пам'ять (а це трапляється рідко), я думаю, що я був на шляху до цього майже рік, перш ніж проект потрапив у CVS.

Оригінальний текст (англ.)LJ: How long have you been developing Icarus Verilog?

SW: My logs show that it was introduced to CVS in November 1998. I had a few false starts for at least two years before then. If memory serves (and it rarely does), I think I was on the current path for close to a year before it got into CVS.

Програма розвивається у відповідності з принципом відкритого програмного забезпечення, у розробці беруть участь всі, хто хоче і може приєднатися до проекту[6]. Навіть логотип Icarus Verilog було зроблено та включено до проекту у відповідності з цим принципом[5]:

LinuxJournal: Ви можете розповісти нам про логотип? Stephen Williams: Звичайно. Стів Вілсон може розповісти докладніше, але, в загальних рисах, логотип було намальовано дядьком Стіва, відставним художником-графіком. Цей художник, Чарльз Вілсон, подарував композицію з метою представлення Icarus Verilog і я високо ціную внесок. Він використовується досі без змін.

Отже, як ви бачите, рух Open Source поширюється за межі програмного забезпечення.

Оригінальний текст (англ.)LJ: Can you tell us about the logo?

SW: Certainly. Steve Wilson can fill in more details, but basically it was drawn by a retired graphic artist, Steve's uncle. The artist, Charles Wilson, donated the design for the purpose of representing Icarus Verilog, and I appreciate the contribution. It's been used thusly ever since.

So you see, this Open Source Movement has a reach even beyond computer software.

Підтримка стандартів

Стабільна версія 0.9.7[1] підтримує такі стандарти мови Verilog (рівень підтримки можна вибрати ключами компілятора iverilog[7]):

- IEEE 1364–1995 (Verilog-95);

- IEEE 1364–2001 (Verilog-2001);

- IEEE 1364–2005 (Verilog-2005)[8].

За умовчанням використовується версія 2005-го року.

Нестабільна версія 0.10.0 на додаток до перерахованого підтримує мову SystemVerilog[9]:

- IEEE 1800–2005 (SystemVerilog-2005);

- IEEE 1800–2009 (SystemVerilog-2009);

- IEEE 1800–2012 (SystemVerilog-2012)[10].

Підтримка стандарту SystemVerilog в процесі розробки, у версії 0.10.0 підтримується лише мала частина можливостей[11].

Для підключення модулів розширення симуляції використовується інтерфейс VPI (англ. Verilog Procedural Interface — інтерфейс процедур Verilog). Модулі мають бути написані на мові C або C++ з використанням інтерфейсу PLI (англ. Programming Language Interface — інтерфейс мов програмування). Обидва інтерфейси описано в стандарті IEEE 1364.

Склад пакета

Пакет Icarus Verilog складається з таких основних програм:

- iverilog

- Власне препроцесор та компілятор мови Verilog. Виконує трансляцію вихідного коду на Verilog у файл програми моделювання або у перелік зв'язків (netlist) для подальшої обробки.

- vvp

- Віртуальна машина, яка виконує програму моделювання, створену компілятором iverilog.

- iverilog-vpi

- Утиліта для спрощення компіляції модулів VPI. Приймає на вході перелік файлів вихідних текстів на мовах C, C++ та об'єктних файлів, на виході видає зібраний vpi-модуль.

Також до пакета входить набір програм конвертації форматів vcd2fst, vcd2lxt, vcd2lxt2, vcd2vzt, vzt2vcd, vztminer, lxt2miner та lxt2vcd.

Використання

Всі програми пакета Icarus Verilog викликаються з командного рядка, режим роботи програм задається ключами[7][12]. В найпростішому варіанті використання в командному рядку компілятора iverilog перераховують лише файли текстів на мові Verilog, наприклад:

iverilog tb.v shiftreg.v

Компліятор згенерує файл програми моделювання з іменем за умовчанням a.out. Цей файл слід передати на виконання симулятору:

vvp a.out

Файл a.out є текстовим файлом, але в операційній системі Лінукс він є виконуваним командним файлом (скриптом) і на його початку у спеціальному форматі записано, яку програму командна оболонка має викликати для інтерпретації:

#! /usr/bin/vvp

:ivl_version "0.9.2 " "(v0_9_2)";

:vpi_time_precision + 0;

:vpi_module "system";

Тому в Лінукс для запуску симуляції достатньо викликати файл a.out як програму:

./a.out

Для спрощення роботи можна створити командний файл або make-файл, в якому записано часто виконувані дії.

Приклад простого проекту

Як приклад розглянемо симуляцію 5-розрядного регістру зсуву, в якому циркулюють два одиничних біти:

module shiftreg (

input wire clk,

output reg [4:0] q

);

always @(posedge clk) q <= {q[3:0], q[2:1]==0};

endmodule

Регістр не має входу скидання в початковий стан і повинен сам виходити на потрібний режим з будь-якого початкового стану. Тому кореневий файл проекту тестування — випробувальний стенд — крім генерації тактового сигналу містить команди примусового занесення деяких неприпустимих комбінацій у регістр q екземпляра модуля shiftreg з іменем DUT (від англ. Device Under Test, назва екземпляра може бути довільна).

module tb;

reg clk;

wire [4:0] q;

/* Екземпляр модуля shiftreg для тестування */

shiftreg DUT(clk, q);

/* Період тактового сигналу - 10 умовних одиниць часу */

always #5 clk = ~clk;

initial

begin

clk = 1;

@(negedge clk);

/* заносимо неприпустиму комбінацію 10101 */

DUT.q = 5'h15;

repeat(10) @(negedge clk);

/* заносимо неприпустиму комбінацію 01111 */

DUT.q = 5'h0F;

repeat(10) @(negedge clk);

$finish;

end

/* Виводимо на друк (умовний) час та виходи регістра */

initial $monitor("%4d %b", $time, q);

endmodule

Викликаємо компілятор (ключ -o tb заміняє ім'я за умовчанням a.out на tb) і відразу викликаємо програму симуляції. По команді $monitor у випробувальному стенді на термінал виводяться моменти часу, в які змінється стан регістра q, та новий стан регістра. Стан лінії clk нас у даному випадку не цікавив.

$ iverilog -o tb tb.v shiftreg.v $ ./tb 0 xxxxx 5 10101 10 01010 20 10100 30 01000 40 10001 50 00011 60 00110 70 01100 80 11000 90 10001 100 00011 105 01111 110 11110 120 11100 130 11000 140 10001 150 00011 160 00110 170 01100 180 11000 190 10001 200 00011

У результаті симуляції видно, що рядках зі значенням часу 5 та 105 в регістр заносяться неприпустимі комбінації, але через деякий час (в рядках з часом 40 та 130) він виходить на режим, коли в ньому зсуваються дві одинички.

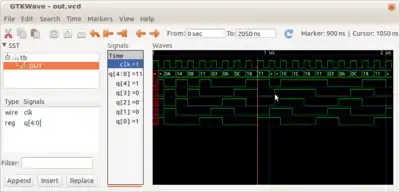

Таким чином — переглядом виходу симулятора в консолі — можна лише нашвидкоруч перевірити прості рішення. Для перегляду діаграм у графічному вигляді слід у файлі випробувального стенду замінити рядок з initial $monitor(...); таким кодом:

/* Виводимо всі внутрішні сигнали об’єкта DUT у vcd-файл */

initial

begin

$dumpfile("out.vcd");

$dumpvars(0,DUT);

end

У процесі симуляції буде створено файл out.vcd, який можна буде переглянути програмою GTKWave.

Додаткові можливості

Компілятор iverilog має ключ -t (target), яким можна задати тип компіляції (кодогенерації). За умовчанням використовується тип цільового файлу vvp, тобто генерація коду для віртуальної машини vvp, цей варіант описано вище.

Вказавши іншу ціль, можна виконати такі дії:

Перевірка синтаксису

Ціль null (ключ -t null) вимикає власне кодогенерацію, проводиться лише аналіз вхідних файлів. Цю ціль зручно використовувати для перевірки синтаксису протягом редагування файлів проекту.

Генерація VHDL-файлу

Ціль vhdl (ключ -t vhdl) призначено для конвертації Verilog-файлів у відповідний їм VHDL-код. Наприклад:

iverilog -t vhdl -o shiftreg.vhdl shiftreg.v

Цей виклик компілятора з файлом shiftreg.v з описаного вище прикладу створить файл shiftreg.vhdl

-- This VHDL was converted from Verilog using the

-- Icarus Verilog VHDL Code Generator 0.9.2 (v0_9_2)

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use std.textio.all;

-- Generated from Verilog module shiftreg (shiftreg.v:1)

entity shiftreg is

port (

clk : in std_logic;

q : out unsigned(4 downto 0)

);

end entity;

-- Generated from Verilog module shiftreg (shiftreg.v:1)

architecture FromVerilog of shiftreg is

signal q_Reg : unsigned(4 downto 0);

begin

q <= q_Reg;

-- Generated from always process in shiftreg (shiftreg.v:6)

process (clk) is

begin

if (rising_edge(clk)) then

q_Reg <= (q_Reg(0 + 3 downto 0) & (q_Reg(1 + 1 downto 1) = "00"));

end if;

end process;

end architecture;

Встановлення програми

Встановлення програми Icarus Verilog може бути виконане двома способами — встановлення готових виконуваних файлів та самостійне збирання з вихідних текстів.

Встановлення двійкових файлів

Для перерахованих вище операційних систем існують вже готові пакунки Icarus Verilog.

Для Unix-подібних ОС як сам Icarus, так і необхідна для зручної роботи програма перегляду GTKWave присутні у сховищі програм цих систем. Збирання, тестування та оновлення пакунків проводить група підтримки відповідного дистрибутиву. Встановити програми можна, користуючись менеджером пакунків системи, наприклад, в Ubuntu можна скористатися графічним інтерфейсом до менеджера пакунків Synaptic або встановити необхідні програми з командного рядка командою:

sudo apt-get install verilog gtkwave

Для Windows підтримку збирання пакетів взяв на себе Pablo Bleyer Kocik. З його сайту можна завантажити інсталятори[13] стабільних версій програми й так званий development snapshot — результат компіляції «знімка» стану вихідних кодів програми на певну дату, який включає в себе найсвіжіші можливості програми, але може працювати нестабільно. До складу інсталяторів включено і Windows-версію програми GTKWave. Програми зібрано пакетом MinGW. Встановлення додаткових компонентів не потрібне.

Компіляція з вихідного коду

Icarus Verilog є консольною програмою, написаною таким чином, щоб мінімально залежати від операційної системи. Проте, програму розраховано на оточення UNIX-подібних систем та відповідні бібліотеки. В операційній системі Windows для збирання пакета можна використати середовища MinGW та Cygwin.

Вихідні коди можна отримати з репозиторію IcarusVerilog[14] на сайті GitHub.

У керівництві зі встановлення[15] дано рекомендації щодо компіляції програми для Linux, Windows, FreeBSD, Mac OS X та OpenSolaris.

Примітки

- Примітки до випуску Icarus Verilog 10

- Release 11.0 — 2020.

- Перелік модулів розширення (плагінів) Icarus Verilog (англ.)

- В Лінукс дивись перелік у файлі /usr/share/doc/iverilog/copyright.

- Michael Baxter Open Source in Electronic Design Automation // Linux Journal. — Вип. 82, лютий 2001

- Перелік учасників проекту Icarus Verilog та їх внесок

- Ключі компілятора iverilog (англ.)

- IEEE Standard for Verilog Hardware Description Language

- Див. файли документації iverilog,

man iverilogу Лінукс та файлC:\iverilog_devel\share\man\man1\iverilog.1у Windows - IEEE Standard for SystemVerilog — Unified Hardware Design, Specification, and Verification Language

- Перелік стандартів, згідно яких проводиться розробка IcarusVerilog

- Ключі віртуальної машини симулятора vvp (англ.)

- Icarus Verilog для Windows

- Сховище проекту IcarusVerilog на сайті GitHub

- Керівництво по встановленню Icarus Verilog (англ.)

Посилання

- Офіційний сайт Icarus Verilog (англ.);

- Wiki проекту Icarus Verilog (англ.) на сайті Wikia;

- Сховище вихідних кодів проекту IcarusVerilog на сайті GitHub;

- Сторінка Icarus Verilog (англ.) на сайті SourceForge.net;

- Icarus Verilog для Windows (англ.) на персональному сайті Pablo Bleyer Kocik.

- Michael Baxter Open Source in Electronic Design Automation // Linux Journal, Вип. 82, лютий 2001 (англ.)

- Stephen Williams, Michael Baxter Icarus Verilog: Open-Source Verilog More Than a Year Later // Linux Journal, Вип. 99, липень 2001 (англ.)