І-НЕ (логічний вентиль)

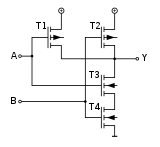

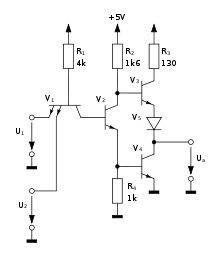

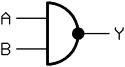

I-НЕ (англ. Not AND, NAND) — логічний вентиль, який реалізує операцію кон'юнкція з інверсією результату. Ця операція також носить назву штрих Шефера. Активний сигнал («логічна 1», «істина») на виході цього вентиля присутній тоді, коли на хоча б на одному його вході присутній пасивний сигнал («логічний 0», «хиба»). Лише коли на обох входах сигнал активний, на виході буде пасивний сигнал.

| І-НЕ (NAND) | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Позначення на схемах | |||||||||||||||||||

| |||||||||||||||||||

| Таблиця істинності | |||||||||||||||||||

| |||||||||||||||||||

В нотації алгебри логіки дія цього вентиля записується формулою:

Умовні позначення

Існує два основних умовних графічних позначень вентиля І-НЕ на принципових схемах, описані в стандартах IEC 60617-12:1997 і ANSI 91-1984. Стандарт DIN 40700 застарів, але описані в ньому символи досі зустрічаються у схемах. Позначення логічних вентилів згідно ДСТУ ГОСТ 2.743-91 «Позначення умовні графічні в схемах. Елементи цифрової техніки» (частина ЄСКД) мають незначні відмінності від стандарту IEC 60617-12.

| IEC 60617-12:1997 | ANSI 91-1984 | DIN 40700 (до 1976) |

|---|---|---|

|

|

Реалізація

Релейно-контактні схеми

Релейно-контактна логіка здійснює операції шляхом формування за допомогою контактів перемикачів або реле кіл для протікання електричного струму, який, у свою чергу, активує наступні реле або живить виходи схеми.

Для реалізації функції NAND нормально-замкнені контакти обох реле з'єднуються паралельно. Якщо не активоване хоча б одне реле, то струм проходитиме через його контакт. Якщо активувати обидва, ланцюг струму буде розірвано, тобто струм не проходить, коли спрацювало реле А і реле B.

Джерела

- Хоровиц, П. Исскусство схемотехники : [рос.] = The Art of Electronics: Second Edition : в 3 т. / П. Хоровиц, У. Хилл ; пер. с англ.: Б. Н. Бронина, И. И. Короткевич [и др.]. — Изд. 4-е, перераб. — М. : Мир, 1993. — Т. 2. — 371 с. — ISBN 5-03-002338-0.

Посилання

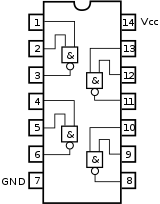

- Документація на мікросхему HEF4011B (4 елементи 2І-НЕ, технологія КМОП) фірми NXP Semiconductors

- Документація на мікросхему SN74AS00 (4 елементи 2І-НЕ, технологія ТТЛШ) фірми Texas Instruments