Рівень передачі регістрів

У Проєктуванні цифрових мікросхем, рівень передачі регістрів (англ. register-transfer level, RTL) це абстрація проєктування, за допомогою якої моделюють синхронні цифрові мікросхеми з точки зору потоку цифрових сигналів (даних) між апаратними регістрами, і логічних операцій, що виконуються над цими сигналами.

Рівень передачі регістрів як абстракція використовується в мовах опису апаратури (англ. hardware description language, HDL) до яких відносяться Verilog та VHDL для створення високорівневого представлення схеми, з якого можна отримати низькорівневе представлення та в остаточному підсумку фактична схема з'єднань. Проєктування на RTL рівні є типовою практикою при розробці сучасних цифрових мікросхем.[1]

RTL описання

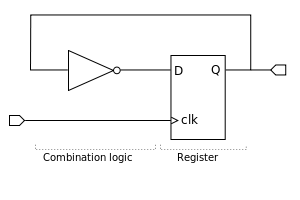

Синхронне коло як складається із двох типів елементів: регістрів (Послідовна логіка) і комбінаційної логіки. Регістри (як правило реалізовані як D тригери) синхронізують роботу схеми із зростаючими фронтами синхроімпульсу, і які є єдиними елементами схеми, що мають властивість пам'яті. Комбінаційна логіка виконує всі логічні функції у схемі і як правило складається із логічних вентилів.

На зображені показано просту синхронну схему. До виходу тригера Q під'єднано інвертор, вихід якого, в свою чергу, з'єднано з D-входом того самого тригера. Це дозволяє створити схему яка змінює свій стан на кожному зростаючому фронті синхроімпульса, clk. В цій схемі комбінаційна логіка складається з одного інвертора.

При проєктуванні цифрових інтегрованих схем за допомогою мови опису апаратури, проєктування як правило здійснюється на вищому рівні абстракції ніж транзисторний рівень (сімейства інтегральних схем логіки) або рівень логічних вентилів. На рівні HDL розробник декларує регістри (які грубо кажучи відповідають поняттю змінних в комп'ютерних мовах програмування), і описує комбінаторну логіку з використанням конструкцій, схожих на конструкції мов програмування, таких як if-then-else і арифметичні оператори. Цей рівень називається рівнем передачі регістрів. Термін відображає зміст того, що RTL приділяє увагу описанню потоку сигналів між регістрами.

Розглянуту вище схему можна також описати за допомогою мови VHDL наступним чином:

D <= not Q;

process(clk)

begin

if rising_edge(clk) then

Q <= D;

end if;

end process;

Використовуючи програми проєктування електронних систем для синтезу, це описання як правило можна напряму перекласти у еквівалентну апаратну реалізацію у вигляді файлу для ASIC або FPGA. Інструмент синтезу також здійснює оптимізацію логіки.

Деякі типи схем на рівні передачі регістрів можна легко упізнати. Якщо існує циклічний шлях логіки від виходів регістрів до їх входу (або від виходів множини регістрів до їх входів), така схема називається скінченним автоматом або представляє послідовну логіку. Якщо існують шляхи логіки від одних регістрів до інших без циклу, це називають конвеєром.

Примітки

- Frank Vahid (2010). Digital Design with RTL Design, Verilog and VHDL (вид. 2nd). John Wiley and Sons. с. 247. ISBN 978-0-470-53108-2.