Секційний процесор

Секційний процесор (англ. bit slicing CPU) — центральний процесор, сконструйований з модулів, або секцій, з меншою розрядністю, ніж розрядність самого процесора (наприклад, 32-розрядний процесор, збудований з чотирьох 8-розрядних модулів). Теоретично можливим є n-секційний процесор.

| Біт |

|---|

| Застосунок |

| Точність двійкової рухомої коми |

| Точність десяткового числа з рухомою комою |

|

Секційні процесори були популярні у мінікомп'ютерах 1960-1980-х років, але поступилися мікропроцесорам, що реалізовуються у вигляді одного кристалу і є суттєво дешевшими при масовому виробництві. З виникненням і розвитком квантових комп'ютерів, спостерігається деяке поновлення інтересу до секційного підходу, зокрема при проектуванні квантових арифметично-логічних пристроїв. Програмно реалізований варіант секційної архітектури знаходить застосування у криптографії.[1]

Архітектура

Секційні процесори, як правило, базуються на мікросхемах чи елементах Арифметико-логічного пристрою (АЛП) розрядності 1, 2, 4, 8 або 16 біт, а також схемах реалізації допоміжних сигналів (наприклад, переносу чи переповнення), що є внутрішніми у мікропроцесорах. Розрядність секцій не обов'язково повинна мати степінь двійки, наприклад, три 1-розрядних АЛП можуть використовуватись як основа для 3-розрядного процесора.[2]

Логіка керування сигналами процесора і АЛП реалізується, як правило, з використанням мікросеквенсера або керуючого ПЗП.

Історичні відомості

Секціонування використовувалося у комп'ютерах ще до появи інтегральних схем (хоча даний термін і не використовувався). Однією з перших секційних машин була EDSAC 2, збудована у математичній лабораторії Кембриджського університету у 1956—1958 роках.[джерело?]

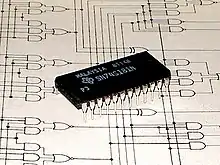

Мейнфрейми серії UNIVAC 1100 мали 36-розрядну архітектуру, і починаючи з моделі 1100/60 (1979 рік) використовували дев'ять 4-розрядних мікросхем АЛП Motorola MC10800[3][4]

Технологія інтегральних схем 1960-1970-х років була значно дорожчою, ніж у 21-му столітті. Ідея використання кількох дешевших мікросхем АЛП меншої розрядності замість однієї дорогої швидко знайшла своє застосування. Типові процесори того часу, на зразок DEC PDP-11 чи Data General Nova мали розрядність 16 біт, пізніше з'явилися і 32-розрядні секційні машини (наприклад, деякі варіанти VAX).

Конструювання процесорів з секцій широко використовувалося у академічному середовищі, і дозволяло студентам збудувати ЦП власної архітектури з мікросхем (наприклад, 74181), які можна придбати у вільному продажу.

Комп'ютер Xerox Alto також мав секційний процесор унікальної архітектури, де мікропрограмування було доступне користувачеві.

Секційні АЛП 1970-1980-х років були збудовані на основі біполярної ТТЛ-технології, що дозволяло отримати непогані показники швидкодії, значно кращі, ніж у мікросхем КМОН тих років.

Відомі реалізації

- 2-розрядні секції:

- 4-розрядні секції:

- National GPC/P / IMP-4 (1973),[7] також вироблявся Rockwell Semiconductor

- Сімейство National IMP-16 (1973), наприклад IMP-00A/520D (RALU) + IMP16A/521D/522D, каскадується до 16-біт

- AMD Am2900 family (1975), наприклад AM2901, AM2903

- Сімейство Monolithic Memories 5700/6700 (1974)[8][9], наприклад MMI 5701 / MMI 6701[10][11] (також вироблявся ITT Semiconductors)

- Texas Instruments SBP0400 (1975), каскадується до 16-біт

- Texas Instruments SN74181 (1970)

- Texas Instruments SN74S281 + SN74S282

- Texas Instruments SN74S481 + SN74S482 (1976)[12]

- Fairchild 9400 (MACROLOGIC), 4700

- Сімейство Motorola M10800 (1979),[3] наприклад MC10800

- 8-розрядні секції:

- Сімейство National Semiconductor IMP-8 (1974), каскадується до 32-біт

- Texas Instruments SN54AS888 / SN74AS888

- Fairchild 100K

- ZMD U830C (1978/1981), каскадується до 32-біт

- 16-розрядні секції:

- Сімейство AMD Am29100

- Synopsys 49C402

Сучасне використання

Програмний підхід

Наприкінці 1990-х років було запропоновано використовувати поняття bit-slicing для реалізації віртуальних паралельних машин на основі ЦП загального призначення. Така машина може застосовуватись, наприклад, для обчислення операцій SIMD довільної ширини. Така технологія інколи називається SWAR (англ. SIMD Within A Register)[13]. Одне з застосувань SWAR — криптографія (наприклад, DES[14]).

Квантові комп'ютери

Було запропоновано ідею реалізацію комп'ютера з тактовою частотою 50 ГГц, що складається з 4-розрядних надпровідникових секцій АЛП.[15]

Джерела

- Benadjila, Ryad; Guo, Jian; Lomné, Victor; Peyrin, Thomas (21 березня 2014). Implementing Lightweight Block Ciphers on x86 Architectures. Cryptology Archive Report 2013/445.

- How to Create a 1-bit ALU. Cs.umd.edu. Процитовано 5 листопада 2017. «Here's how you would put three 1-bit ALU to create a 3-bit ALU»

- The MC10800. 6502.org. Процитовано 5 листопада 2017.

- Archived copy. Архів оригіналу за 11 червня 2016. Процитовано 28 січня 2016.

- 3002 - The CPU Shack Museum. Cpushack.com. Процитовано 5 листопада 2017.

- Bipolar microprocessor. Signetics. Архів оригіналу за 12 лютого 2011. Процитовано 17 лютого 2018.

- IMP-4 - National Semiconductor. En.wikichip.org. Процитовано 5 листопада 2017.

- 6701 - The CPU Shack Museum. Cpushack.com. Процитовано 5 листопада 2017.

- Archived copy. Архів оригіналу за 11 лютого 2011. Процитовано 21 травня 2017.

- 5700/6700 - Monolithic Memories. En.wikichip.org. Процитовано 5 листопада 2017.

- File:MMI 5701-6701 MCU (August, 1974).pdf. En.wikichip.org. Процитовано 5 листопада 2017.

- SN74S481 - The CPU Shack Museum. Cpushack.com. Процитовано 5 листопада 2017.

- Bitslice DES. Darkside.com.au. Процитовано 5 листопада 2017.

- A Fast New DES Implementation in Software. — 1997. — 14 лютого. Процитовано 5 листопада 2017.

- Tang, Guang-Ming; Takata, Kensuke; Tanaka, Masamitsu; Fujimaki, Akira; Takagi, Kazuyoshi; Takagi, Naofumi (January 2016). 4-bit Bit-Slice Arithmetic Logic Unit for 32-bit RSFQ Microprocessors. IEEE Transactions on Applied Superconductivity 26 (1). doi:10.1109/TASC.2015.2507125. 1300106. «[…] 4-bit bit-slice arithmetic logic unit (ALU) for 32-bit rapid single-flux-quantum microprocessors was demonstrated. The proposed ALU covers all of the ALU operations for the MIPS32 instruction set. […] It consists of 3481 Josephson junctions with an area of 3.09 × 1.66 mm2. It achieved the target frequency of 50 GHz and a latency of 524 ps for a 32-bit operation, at the designed DC bias voltage of 2.5 mV […] Another 8-bit parallel ALU has been designed and fabricated with target processing frequency of 30 GHz […] To achieve comparable performance to CMOS parallel microprocessors operating at 2–3 GHz, 4-bit bit-slice processing should be performed with a clock frequency of several tens of gigahertz. Several bit-serial arithmetic circuits have been successfully demonstrated with high-speed clocks of above 50 GHz […]»