FinFET

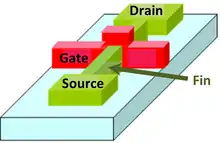

Польовий транзистор з вертикальним затвором (англ. FinFET) — мультизатворний польовий МДН транзистор (MOSFET), побудований на підкладці, де затвор розміщений на двох, трьох чи чотирьох сторонах каналу (обгорнутий навколо каналу), утворюючи подвійну структуру затвору. Ці прилади отримали назву FinFET (англ. fin - плавник, FET(англ. field-effect transistor) - польовий транзистор), оскільки область стоку-витоку утворює "плавники" на поверхні кремнію. Пристрої FinFET мають значно швидший час перемикання та більш високу густину струму, ніж плоска технологія КМОН (CMOS) (комплементарний метал-оксид-напівпровідник).

FinFET — це тип непланарного транзистора, або "3D" транзистора. [1] Це основа для виготовлення сучасних наноелектронних напівпровідникових пристроїв. Мікрочипи, що використовують затвор FinFET, вперше були комерціалізовані в першій половині 2010-х років і стали домінуючою конструкцією затвору на 14-нм, 10-нм та 7-нм технологічних процесах .

Історія

20 років після того, як MOSFET був вперше продемонстрований Мохамедом Аталлою та Доуном Кангом з Bell Labs в 1960 році [2] концепція MOSFET з подвійним затвором була запропонована Тошихіро Секігавою в патенті 1980 року, що описує планарний XMOS транзистор. [3] Секігава виготовив транзистор XMOS з Ютакою Хаяші в 1984 році. Вони продемонстрували, що ефект "короткого каналу" може бути значно зменшений за допомогою сендвіч структури повністю збідненого кремнію на ізоляторі (FDSOI) між двома електродами затвору, з'єднаними між собою. [4] [5]

Перший тип FinFET транзистора був названий «транзистор із збідненим спертим каналом» або «Дельта» транзистор та був вперше виготовлений в Японії у 1989 році [4] [6] [7] Затвор транзистора може охоплювати та електрично контактувати з напівпровідниковим каналом "плавника" з верхньої та бокової сторони або лише з боків. Перший називається транзистором з потрійним затвором, а другий транзистором з подвійним затвором. Транзистор з подвійним затвором необов'язково має з'єднані обидві сторони, а може мати дві розділені клемами або контакти. Цей варіант називається розділеним транзистором. Таке компонування дозволяє більш досконало керувати роботою транзистора.

Індонезійський інженер Ефенді Леобандунг, працюючи в університеті Міннесоти, опублікував документ зі Стівеном Ю. Чуу на 54-й науково-дослідницькій конференції у 1996 році, в якому виклав переваги утворення CMOS транзистора шляхом побудови мультизатвору на завуженому розділеному каналі для поліпшення масштабування та збільшення струму пристрою за рахунок збільшення його ефективної ширини. [8] Така структура виглядає як сучасний FinFET. Хоча деякими розмірами доводиться жертвувати, розрізаючи канал на частини, провідність бічних "плавників" більша, ніж провідність завуженого каналу. [9] Канал пристрою мав розміри - 35 нм ширина і 70 нм довжина каналу.

Дослідження Діг Хісамото транзисторів DELTA привернули увагу Агенції прогресивних дослідницьких проектів оборони (DARPA), яка в 1997 році уклала контракт з дослідницькою командою Університету Каліфорнії Берклі на розробку субмікронного транзистора на основі технології DELTA. [10] Команда здійснила такі прориви у період 1998 - 2004 р.р. [11]

- 1998 – N-канальний FinFET [12]

- 1999 – P-канальний FinFET [13]

- 2001 – 15 нм FinFET [14]

- 2002 – 10 нм FinFET [15]

- 2004 – затвор High-k - метал FinFET

Вони ввели термін "FinFET" (польовий транзистор з вертикальним затвором) в документі від грудня 2000 року [16] , що містив опис непланарного транзистора з двома затворами, побудованого на підкладці SOI. [17]

У 2006 році команда корейських дослідників з Корейського інституту науково-технічного розвитку (KAIST) та Національного центру нанотехнологій розробила 3 нм транзистор, найменший наноелектронний пристрій у світі, заснований на технології FinFET " затвор увесь навколо" (GAA) . [18] [19] У 2011 році дослідники з Rice University продемонстрували, що FinFET-ти можуть мати два електрично незалежні затвори, що дає дизайнерам схем більшу гнучкість у ефективному проектуванні схем з малопотужними затворами. [20]

Комерціалізація

Перший 25-нанометровий транзистор, що працює всього від 0,7 Вольт, був продемонстрований у грудні 2002 року TSMC . Конструкція "Omega FinFET", названа за схожістю між грецькою літерою "Омега" та формою, яку утворює затвор навколо структури стік - витік та має затримку затвора всього 0,39 пікосекунди (пс) для транзистора N-типу і 0,88 пс для транзистора P-типу.

У 2004 році компанія Samsung продемонструвала дизайн "Bulk FinFET", яка дала змогу масово виробляти пристрої FinFET. Вони продемонстрували динамічну пам'ять з довільним доступом (DRAM) 90 нм на об'ємному FinFET процесі. [11]

У 2011 році Intel продемонструвала транзистори з потрійним затвором, де затвор огортає канал з трьох сторін, що дозволяє підвищити енергоефективність і зменшити затримку затвора, таким чином, збільшити продуктивність, випереджаючи планарні аналоги. [21] [22] [23]

Комерційно виготовлені мікросхеми техпроцесу 22 нм і менше використовували конструкції затворів FinFET. Варіант "Tri-Gate" від Intel на 22 нм техпроцесі був оголошений в 2011 році для мікроархітектури Ivy Bridge . [24] Ці пристрої постачаються з 2012 року.

Починаючи з 2014 року, на 14 нм (або 16 нм) техпроцесі основні підприємства (TSMC, Samsung, GlobalFoundries) використовували технологію FinFET.

У 2013 році SK Hynix розпочав комерційне масове виробництво на 16-ти нм техпроцесі, [25] TSMC почав виробництво на 16-ти нм процесі FinFET, [26] Samsung Electronics почали випуск на 10 нм процесі. [27]

TSMC розпочав виробництво 7 нм процесу в 2017 році [28] , а Samsung почав виробництво на 5 нм техпроцесі в 2018 році. [29]

У 2019 році Samsung оголосила про плани комерційного виробництва на 3 нм техпроцесі GAAFET до 2021 року. [30]

Комерційне виробництво наноелектронної напівпровідникової пам'яті FinFET розпочалося в 2010-х. У 2013 році SK Hynix розпочав серійне виробництво 16-ти нм флеш-пам’яті NAND, [25] та Samsung Electronics розпочали виробництво багаторівневої флеш-пам’яті NAND на 10 нм . [27]

У 2017 році TSMC розпочав виробництво пам'яті SRAM за допомогою 7 нм процесу. [28]

Дивись також

- GAAFET

- Наноелектроніка

- Виробництво напівпровідникових пристроїв

- Кількість транзисторів

Джерела

- What is Finfet?. Computer Hope. 26 квітня 2017. Процитовано 4 липня 2019.

- 1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated. The Silicon Engine. Computer History Museum. Процитовано 25 вересня 2019.

- Koike, Hanpei; Nakagawa, Tadashi; Sekigawa, Toshiro; Suzuki, E.; Tsutsumi, Toshiyuki (23 лютого 2003). Primary Consideration on Compact Modeling of DG MOSFETs with Four-terminal Operation Mode. TechConnect Briefs 2 (2003): 330–333. Архів оригіналу за 26 вересня 2019. Процитовано 27 грудня 2019.

- Colinge, J.P. (2008). FinFETs and Other Multi-Gate Transistors. Springer Science & Business Media. с. 11 & 39. ISBN 9780387717517.

- Sekigawa, Toshihiro; Hayashi, Yutaka (August 1984). Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate. Solid-State Electronics 27 (8): 827–828. ISSN 0038-1101. doi:10.1016/0038-1101(84)90036-4.

- Hisamoto, Digh; Kaga, Toru; Kawamoto, Yoshifumi; Takeda, Eiji (December 1989). A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET. International Technical Digest on Electron Devices Meeting: 833–836. doi:10.1109/IEDM.1989.74182.

- IEEE Andrew S. Grove Award Recipients. IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Процитовано 4 липня 2019.

- Leobandung, Effendi; Chou, Stephen Y. (1996). Reduction of short channel effects in SOI MOSFETs with 35 nm channel width and 70 nm channel length. 1996 54th Annual Device Research Conference Digest: 110–111. ISBN 0-7803-3358-6. doi:10.1109/DRC.1996.546334.

- Leobandung, Effendi (June 1996). Nanoscale MOSFETs and single charge transistors on SOI. Minneapolis, MN: U of Minnesota, Ph.D. Thesis. с. 72.

- The Breakthrough Advantage for FPGAs with Tri-Gate Technology. Intel. 2014. Процитовано 4 липня 2019.

- Tsu‐Jae King, Liu (11 червня 2012). FinFET: History, Fundamentals and Future. University of California, Berkeley. Symposium on VLSI Technology Short Course. Архів оригіналу за 28 травня 2016. Процитовано 9 липня 2019.

- Hisamoto, Digh; Hu, Chenming; Liu, Tsu-Jae King; Bokor, Jeffrey; Lee, Wen-Chin; Kedzierski, Jakub; Anderson, Erik; Takeuchi, Hideki та ін. (December 1998). A folded-channel MOSFET for deep-sub-tenth micron era. International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217): 1032–1034. ISBN 0-7803-4774-9. doi:10.1109/IEDM.1998.746531.

- Hisamoto, Digh; Kedzierski, Jakub; Anderson, Erik; Takeuchi, Hideki (December 1999). Sub 50-nm FinFET: PMOS. International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318): 67–70. ISBN 0-7803-5410-9. doi:10.1109/IEDM.1999.823848.

- Hu, Chenming; Choi, Yang‐Kyu; Lindert, N.; Xuan, P.; Tang, S.; Ha, D.; Anderson, E.; Bokor, J. та ін. (December 2001). Sub-20 nm CMOS FinFET technologies. International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224): 19.1.1–19.1.4. ISBN 0-7803-7050-3. doi:10.1109/IEDM.2001.979526.

- Ahmed, Shibly; Bell, Scott; Tabery, Cyrus; Bokor, Jeffrey; Kyser, David; Hu, Chenming; Liu, Tsu-Jae King; Yu, Bin та ін. (December 2002). FinFET scaling to 10 nm gate length. Digest. International Electron Devices Meeting: 251–254. ISBN 0-7803-7462-2. doi:10.1109/IEDM.2002.1175825.

- Hisamoto, Digh; Hu, Chenming; Bokor, J.; King, Tsu-Jae; Anderson, E. та ін. (December 2000). FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Transactions on Electron Devices 47 (12): 2320–2325. Bibcode:2000ITED...47.2320H. doi:10.1109/16.887014. Проігноровано невідомий параметр

|citeseerx=(довідка) - Hisamoto, Digh; Hu, Chenming; Huang, Xuejue; Lee, Wen-Chin; Kuo, Charles та ін. (May 2001). Sub-50 nm P-channel FinFET. IEEE Transactions on Electron Devices 48 (5): 880–886. Bibcode:2001ITED...48..880H. doi:10.1109/16.918235.

- Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology ). Nanoparticle News. 1 квітня 2006. Архів оригіналу за 6 November 2012. Процитовано 6 липня 2019.

- Lee, Hyunjin (2006). Sub-5nm All-Around Gate FinFET for Ultimate Scaling. Symposium on VLSI Technology, 2006: 58–59. ISBN 978-1-4244-0005-8. doi:10.1109/VLSIT.2006.1705215.

- Rostami, M.; Mohanram, K. (2011). IEEE Xplore Abstract - Dual- Independent-Gate FinFETs for Low Power Logic Circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 30 (3): 337–349. doi:10.1109/TCAD.2010.2097310.

- Bohr, Mark; Mistry, Kaizad (May 2011). Intel's Revolutionary 22 nm Transistor Technology. intel.com. Процитовано 18 квітня 2018.

- Grabham, Dan (6 травня 2011). Intel's Tri-Gate transistors: everything you need to know. TechRadar. Процитовано 19 квітня 2018.

- Bohr, Mark T.; Young, Ian A. (2017). CMOS Scaling Trends and Beyond. IEEE Micro 37 (6): 20–29. doi:10.1109/MM.2017.4241347. «The next major transistor innovation was the introduction of FinFET (tri-gate) transistors on Intel’s 22-nm technology in 2011.»

- Intel 22nm 3-D Tri-Gate Transistor Technology

- History: 2010s. SK Hynix. Процитовано 8 липня 2019.

- 16/12nm Technology. TSMC. Процитовано 30 червня 2019.

- Samsung Mass Producing 128Gb 3-bit MLC NAND Flash. Tom's Hardware. 11 квітня 2013. Процитовано 21 червня 2019.

- 7nm Technology. TSMC. Процитовано 30 червня 2019.

- Shilov, Anton. Samsung Completes Development of 5nm EUV Process Technology. www.anandtech.com. Процитовано 31 травня 2019.

- Armasu, Lucian (11 січня 2019). Samsung Plans Mass Production of 3nm GAAFET Chips in 2021. www.tomshardware.com.