Гарвардська архітектура

Га́рвардська архітекту́ра (англ. Harvard architecture) — архітектура обчислювальних машин, головною відмінністю якої від інших подібних архітектур (див. напр. Архітектура фон Неймана) є те, що дані та оператори (алгоритм) зберігаються окремо. Першим комп'ютером, який застосовував гарвардську архітектуру, був Mark I, який експлуатувався в Гарварді (звідки назва архітектури) та зберігав команди окремо на перфокартах, а дані в релейному запам'ятовуючому пристрої.

Така структура має одну важливу перевагу над фон-нейманівською архітектурою: дані можна завантажувати для обробки з запам'ятовуючого пристрою одночасно з командами. В фон-нейманівській архітектурі для зв'язку операційного та керувального пристроїв (які разом складають центральний процесор), використовується одна шина, тому необхідно спочатку завантажити в процесор команду, а вже потім, звернувшись по тій же шині за адресою, яка вказана в команді — завантажити дані. Наявність в гарвардській архітектурі двох незалежних підсистем пам'яті з окремими шинами дозволяє вести процес завантаження команд і даних практично паралельно.

Головним недоліком гарвардської архітектури є порівняна з фон-нейманівською складність реалізації. Адже для кожного з запам'ятовуючих пристроїв необхідний свій контролер і своя шина, що зі збільшенням розрядності призводить до зростання кількості з'єднань у системі, і це негативно впливає як на складність проектування, так і на швидкодію.

Гарвардська архітектура широко застосовується в спеціалізованих обчислювачах, зокрема в мікроконтролерах та цифрових сигнальних процесорах, де необхідний високоінтенсивний обмін даними. Також за гарвардською архітектурою зазвичай організується кеш-пам'ять в ЕОМ загального призначення, яка розділяється окремо на кеш-пам'ять команд та кеш-пам'ять даних (але, точніше, це стосується внутрішньої організації процесора, а не архітектури ЕОМ).

Історія

У 1930-х роках уряд США доручили Гарвардському та Принстонському університету Розробити архітектуру ЕОМ для військово-морської артилерії. Напрікінці 1930-х років у Гарвардському університеті Говардом Ейкеном була розроблена архітектура комп'ютера Марк I, надалі звана по імені цього університету. У жовтні 1937 року оригінальна ідея була продемонстрована Ейкеном для компанії IBM[1]. Однак перемогла більш проста у реалізації розробка Принстонського університету, відома як архітектура фон Неймана.

Гарвардська архітектура використовувалася радянським ученим А. І. Кітовим в ВЦ-1 МО СРСР[2].

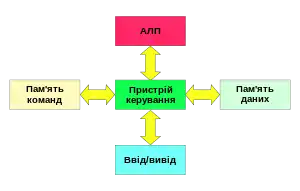

Класична гарвардська архітектура

Типові операції (додавання та множення) вимагають від будь-якого обчислювального пристрою кількох дій:

- вибірку двох операндів;

- вибір інструкції та її виконання;

- збереження результатів.

Ідея, реалізована Ейкеном, полягала у фізичному поділі ліній передачі команд та даних. У першому комп'ютері Ейкена «Марк I» для зберігання інструкцій використовувалася перфострічка, а для роботи з даними — електромеханічні регістри. Це дозволяло одночасно пересилати й обробляти команди і дані, завдяки чому значно підвищувалася загальна швидкодія комп'ютера.

У гарвардській архітектурі характеристики пристроїв пам'яті для інструкцій і пам'яті для даних не обов'язково повинні бути однаковими. Зокрема, ширина слова, тактування, технологія реалізації та структура адрес пам'яті можуть розрізнятися. У деяких системах інструкції можуть зберігатися в пам'яті тільки для читання, в той час як для збереження даних зазвичай потрібно пам'ять з можливістю читання і запису. У деяких системах потрібно значно більше пам'яті для інструкцій, ніж пам'яті для даних, оскільки дані зазвичай можуть довантажуватися з зовнішньої або більш повільної пам'яті. Така потреба збільшує бітність (ширину) шини адреси пам'яті інструкцій в порівнянні з шиною адреси пам'яті даних.

Відмінність від архітектури фон Неймана

У чистій архітектурі фон Неймана процесор в кожен момент часу може або читати інструкцію, або читати/записувати одиницю даних з/в пам'ять. Обидві дії одночасно відбуватися не можуть, оскільки інструкції і дані використовують один і той же потік (шину). У комп'ютері з використанням гарвардської архітектури процесор може читати інструкції і виконувати доступ до пам'яті даних одночасно, без використання кеш-пам'яті. Таким чином, комп'ютер з гарвардською архітектурою при певній складності схеми працює швидше, ніж комп'ютер з архітектурою фон Неймана, оскільки шини інструкцій і даних розташовані на різних, не пов'язаних між собою фізично, каналах.

Виходячи з фізичного поділу шин команд і даних, розрядності цих шин (отже, і адресні простори) можуть мати різні значення і фізично не можуть перетинатися один з одним.

Модифікації

Модифікована Гарвардська архітектура

Відповідна схема реалізації доступу до пам'яті має один очевидний недолік — високу вартість. При поділі каналів передачі команд і даних на кристалі процесора останній повинен мати майже вдвічі більше виводів, так як шина адреси і шина даних складають основну частину виводів мікропроцесора. Способом вирішення цієї проблеми стала ідея використовувати загальні шину даних і шину адреси для всіх зовнішніх даних, а всередині процесора використовувати шину даних, шину команд і дві шини адреси. Таку концепцію стали називати модифікованою гарвардською архітектурою.

Такий підхід застосовується в сучасних сигнальних процесорах. Ще далі по шляху зменшення вартості пішли при створенні однокристальних ЕОМ — мікроконтролерів. У них одна шина команд і даних застосовується і всередині кристала. Поділ шин в модифікованій гарвардській архітектурі здійснюється за допомогою роздільних керувальних сигналів: читання, запису або вибору області пам'яті.

Розширена Гарвардська архітектура

Часто потрібно вибрати три складові: два операнди та інструкцію (в алгоритмах цифрової обробки сигналів це найбільш поширена задача в ШПФ, FIR-фільтри та РФ). Для цього існує кеш-пам'ять. У ній може зберігатися інструкція — отже, обидві шини залишаються вільними і з'являється можливість передати два операнда одночасно. Використання кеш-пам'яті разом з розділеними шинами отримало назву «Super Harvard Architecture» («SHARC») — розширена Гарвардська архітектура. Прикладом можуть служити процесори «Analog Devices»: ADSP-21xx — модифікована Гарвардська архітектура, ADSP-21xxx (SHARC) — розширена Гарвардська архітектура.

Гібридні модифікації з архітектурою фон Неймана

Існують гібридні архітектури, що поєднують переваги як гарвардської, так і фон-неймановской архітектур. Сучасні CISC — процесори мають роздільної кеш-пам'яттю 1-го рівня для інструкцій і даних, що дозволяє їм за один робочий такт отримувати одночасно і команду, і дані для її виконання. Тобто процесорне ядро, формально, є гарвардським, але програмно воно фон-Неймановське, що спрощує написання програм. Зазвичай в даних процесорах одна шина використовується і для передачі команд, і для передачі даних, що спрощує конструкцію системи. Сучасні варіанти таких процесорів можуть іноді містити вбудовані контролери відразу декількох різнотипних шин для роботи з різними типами пам'яті — наприклад, DDR RAM і Flash. Тим не менше, і в цьому випадку шини, як правило, використовуються і для передачі команд, і для передачі даних без поділу, що робить дані процесори ще більш близькими до фон-неймановскої архітектурі при збереженні плюсів гарвардської архітектури.

Використання

Першим комп'ютером, в якому була використана ідея гарвардської архітектури, був Марк I.

Гарвардська архітектура використовується в ПЛК та мікроконтролерах, таких, як Microchip PIC, Atmel AVR, Intel 4004, Intel 8051, а також в кеш-пам'яті першого рівня x86-мікропроцесорів, діляться на два рівних або різних за обсягом блоку для даних і команд.

Примітки

- Bernard Cohen. Howard Aiken, Portrait of a computer pioneer. — Cambridge, Massachusetts : The MIT Press, 2000. — С. 53. — ISBN 978-0-2625317-9-5.

- ВЦ-1 МО СССР, 1958[недоступне посилання з квітня 2019]