Coreboot

Coreboot (раніше LinuxBIOS) — проєкт зі створення вільних прошивок і BIOS, схвалений Free Software Foundation. Метою проєкту є заміна власницьких і закритих BIOS, використовуваних більшістю персональних комп'ютерів, на легковаговий BIOS, призначений виключно для завантаження і запуску сучасних 32- і 64-розрядних операційних систем. Проєкт LinuxBIOS був початий взимку 1999 в лабораторії Advanced Computing Laboratory в Лос-Аламосі. Результати роботи проєкту поширюються на умовах GNU GPL.

| |

coreboot | |

| Тип | Firmware |

|---|---|

| Автор(и) | Ronald G. Minnich, Eric Biederman, Olli Lo, Stefan Reinauer, спільнота coreboot |

| Перший випуск | 1999 |

| Стабільний випуск | 4.13 (20 листопада 2020) |

| Репозиторій | review.coreboot.org/cgit/coreboot.git |

| Платформа | x86 х86-64, ARMv7[1] |

| Мова програмування | головним чином C, лише близько 1 % ASM |

| Стан розробки | активний |

| Ліцензія | GPLv2 |

| Вебсайт | coreboot.org |

Загальні відомості

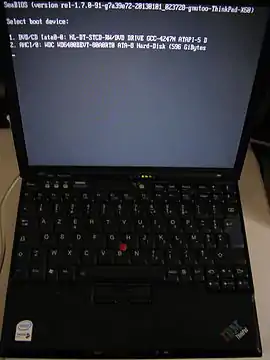

Типова задача coreboot — завантажувати ядро Linux, але, крім цього, coreboot може завантажувати і запускати виконувані файли в форматі ELF, зазвичай звані «корисним завантаженням» (англ. payload). Корисними завантаженнями можуть виступати, наприклад, iPXE, який здатний завантажити Linux по мережі або SeaBIOS — вільна реалізація BIOS, що дозволяє завантажувати Windows 2000/XP/Vista/7 і *BSD системи (раніше для цього використовувалася завантаження ADLO). Coreboot може завантажити операційну систему з будь-якого підтримуваного пристрою, такого як Myrinet, QsNet або SCSI.

Coreboot виконує ініціалізацію апаратного забезпечення, яку не може виконати операційна система, після чого передає управління ядру ОС, надаючи йому можливість завершити ініціалізацію апаратури.

Coreboot підтримує платформи PowerPC і x86.

Унікальною особливістю coreboot є те, що версія для x86 починає працювати в 32-розрядному режимі після виконання всього лише шістнадцяти інструкцій процесора, тоді як типові BIOS для платформи x86 працюють виключно в 16-розрядному режимі. Робота в 32-розрядному режимі робить завантаження з LinuxBIOS дуже швидким (нині[коли?] рекорд холодного старту з LinuxBIOS становить близько 3 секунд).

Хоча у назві LinuxBIOS присутнє слово Linux, LinuxBIOS може завантажувати ядра інших операційних систем. Наприклад, LinuxBIOS може безпосередньо завантажувати ядро Plan 9. Тому він був перейменований в coreboot.

Корисне завантаження

Coreboot сам по собі є лише маленькою програмою, що виконує ініціалізацію обладнання на материнській платі, далі управління передається одній з програм корисного завантаження:

- SeaBIOS — вільна реалізація BIOS, що підтримує стандартні системні виклики. Дозволяє завантажувати операційну систему з твердого диска або CD/DVD дисковода. На даний момент випробувана з ОС Linux, NetBSD, FreeDOS, і Windows XP/Vista/7. Завантаження інших x86-сумісних операційних систем також повинне працювати.

- ADLO — реалізація BIOS, що використовує напрацювання проєкту Bochs з підтримкою більшості стандартних системних викликів. Дозволяє завантажувати Windows 2000, OpenBSD. В даний час витіснена SeaBIOS.

- GRUB — популярний завантажувач ОС, що дозволяє завантажувати ядра дуже багатьох операційних систем (зокрема Linux) з широкого діапазону файлових систем, і що володіє безліччю додаткових функцій.

- LILO — простий завантажувач ОС з підтримкою файлових систем.

- Etherboot — мережевий завантажувач ОС, що дозволяє завантажувати ОС по мережі в рамках технології PXE.

- OpenBIOS і Open Firmware — вільні реалізації BIOS.

- Ядро Linux — також може виступати як корисне завантаження.

- TianoCore — вільна реалізація UEFI.

Розробка та налагодження coreboot

Оскільки coreboot повинен ініціалізувати апаратуру, то він повинен бути адаптований для підтримки кожного системного контролера (чипсета) і кожної плати на основі такого контролера. Додавання підтримки будь-якої нової плати ускладнюється труднощами налагодження: налагоджувальна інформація виводиться за допомогою тих чи інших апаратних засобів, але як організувати виведення, коли засоби виведення ще не ініціалізовані?

Coreboot використовує декілька пристроїв і прийомів для спрощення налагодження:

- Перед ініціалізацією оперативної пам'яті coreboot ініціалізує послідовний інтерфейс, який може бути використаний для виведення налагоджувальної інформації на підключений до нього емулятор термінала.

- Використовується POST-карта — пристрій, що підключається до шини розширення комп'ютера і містить дисплей, який може виводити інформацію, зазвичай, це дві цифри в шістнадцятковій системі числення. Програмна робота з таким пристроєм досить проста, наприклад, на архітектурі x86 достатньо записати байт, який необхідно відобразити на індикаторі POST-карти, за адресою 0x80 в адресному просторі пристроїв введення-виведення.

- Пристрій BIOS Savior, що являє собою дві мікросхеми ПЗП, які містять BIOS і можливість вибрати для роботи одну з них. Дорожчою альтернативою такому пристрою є використання програматора мікросхем ПЗП.

- Апаратний емулятор центрального процесора або підключення до центрального процесора через інтерфейс JTAG, дозволяє таким чином знати результат роботи кожної інструкції центрального процесора на початкових етапах роботи комп'ютера.

Ініціалізація ОЗП

Найскладнішою частиною coreboot є код, який ініціалізує оперативну пам'ять і її контролер. Справа в тому, що поки ОЗП не ініціалізований, його неможливо використовувати. Очевидним способом ініціалізації контролера ОЗП і самої оперативної пам'яті без звернень до неї є використання регістрів загального призначення процесора. Для спрощення цього складного завдання був розроблений спеціальний компілятор мови C — romcc, який породжує код, що під час виконання не здійснює звернень до оперативної пам'яті. За допомогою romcc компілюється код, який ініціалізує ОЗП шляхом звернення до SPD ROM на модулях DIMM по шині SMBus. Після виконання даного коду ОЗП можна використовувати.

Підтримувані платформи

Крім x86 і x86-64, Coreboot підтримує процесори AMD Geode. Підтримка почалася з процесора з Geode GX, розробленого AMD для OLPC, Artec Group потім додана підтримка Geode LX для своєї моделі DBE61 ThinCan. Нещодавно, код був прийнятий AMD і далі удосконалений для OLPC після переходу на платформу Geode LX. Цей код нині є подальшим розвитком у Coreboot спільноті щоб підтримати інші рішення AMD Geode. Coreboot можуть бути прошиті на платформі AMD Geode за допомогою Flashrom.

З цього початкового розвитку на платформах на базі AMD Geode, Coreboot підтримка була розширена для багатьох процесорів AMD і чипсетів. Список процесорів включає сім'ю 0Fh і 10h K8, також Family 14h на ядрі Bobcat, AMD APU. Coreboot підтримка поширюється також на чипсетах AMD серій RS690, RS7xx, SB600 і SB8x.

Примітки

- Coreboot ARM. coreboot. 15 жовтня 2013. Процитовано 1 лютого 2014.

Див. також

- Open Firmware

- OpenBIOS

- Extensible Firmware Interface

Посилання

- Домашня сторінка coreboot.org, а також wiki(англ.)

- Motherboards supported in coreboot v2(англ.)

- відкриття системи BIOS для Linux

- LinuxBIOS: комп'ютер з Лінукс в серці А. Кухар (квітень 2004)

- Open BIOSes for Linux (англ.) IBM

- Google Linux BIOS(рос.) LOR 2006

- інтерв'ю з Ronald G. Minnich, одним з основних розробників проєкту LinuxBIOS