Nios II

Nios II — архітектура 32-розрядного програмного мікропроцесора RISC від компанії Altera. Архітектура спеціально спроектована і оптимізована для FPGA Altera, і є розвитком попередньої 16-бітної архітектури Nios. Починаючи з FPGA Altera Quartus підтримується модуль керування пам'яттю (англ. Memory Management Unit — MMU), що забезпечує запуск операційної системи, наприклад Linux.[1] Без MMU на процесорі можна запустити спрощені операційні системи, такі як FreeRTOS або µClinux.

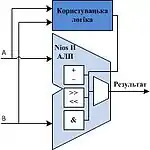

До ключових особливостей процесора відносять можливість вбудовувати додаткову логіку за допомогою користувацьких команд.

Версії

Процесор Nios II забезпечує високий ступінь гнучкості, оскільки Altera пропонує три версії системи, що різняться експлуатаційними вимогами, вартістю та площею кристалу. Nios II/f (fast) призначений для забезпечення високої продуктивності виконання, Nios II/e (economy) забезпечує найменший розмір самого ядра і підходить для застосувань, що вимагають простої логіки керування. Середнє положення між ними займає Nios II/s (standard), адже використовується на 20% менше логічних елементів та ресурсів плати, ніж Nios II/f за рахунок продуктивності (на 40% ніж Nios II/f).

Властивості Nios

- окремі кеші для команд та даних, розміри яких визначаються користувачем: від 512 байт до 64 КБ;

- додатковий MMU для підтримки операційних систем, які цього вимагають;

- додатковий блок захисту пам'яті (англ. Memory Protection Unit — MPU) для підтримки операційних систем і середовищ виконання, які мають механізм захисту пам'яті, але не потребують віртуальної пам'яті;

- доступ до 2 ГБ (за відсутності MMU), або 4 гігабайті (коли MMU присутній) віртуального адресного простору, поділеного на розділи: верхні 2 ГБ зарезервовані для операційної системи, а нижні 2 — для користувацьких процесів. З пам'яті, виділеної для операційної системи, 512 МБ необхідно для доступу до периферійних пристроїв, ще 512 відведено для її ядра, решта використовується TLB і процесами ядра;

- підтримка інтерфейсу додаткового контролеру зовнішніх переривань (англ. External Interface Controller — EIC), що забезпечує налаштування пріоритетів переривань;

- підтримка додаткових наборів тіньових регістрів для зменшення затримки при обробці переривань;

- шестиступінчатий конвеєр та динамічне прогнозування переходів;

- апаратні команди множення, ділення та зсуву для збільшення ефективності арифметичних інструкцій;

- підтримка додавання користувацьких команд;

- підтримка модуля налагодження JTAG та апаратних точок зупинки.

Набір команд

Усі команди процесора є 32-розрядними та діляться на три типи: I, R та J. Команди першого класу мають константи, записані в командному слові. В командах другого типу всі аргументи та результати визначаються через номери регістрів. Нарешті, останній клас команд має 26-бітне поле констант, що використовуються як адреси переходу.

Інструкції передавання даних

Процесор Nios II реалізує типову архітектуру load/store («завантажити/зберегти»), тому всі переміщення даних між регістрами, пам'яттю та периферійними пристроями виконуються цими командами. Пам'ять та периферійні пристрої поділяють загальний адресний простір.

Арифметичні й логічні команди

Дані для арифметично-логічного блоку мікропроцесора зберігаються в регістрах загального призначення, а після виконання операції, результат зберігається теж в регістрі.

Логічні операції представлені операціями І, АБО, ВИКЛЮЧНЕ АБО та НЕ, арифметичні включають команди додавання, віднімання. Також існує одна команда виконання множення 32-бітних операндів та ділення (з 32-розрядним результатом) та спеціалізовані команди для множення 64- та 128-бітних чисел.

Ядро Nios II надає кілька варіантів для підвищення продуктивності множення, ділення та операцій зсуву. Їх реалізація залежить від особливостей цільової платформи: наприклад, в ПЛІС Altera для прискорення можуть бути задіяні апаратні перемножувачі.

Інструкції move

Ці команди забезпечують переміщення операндів, копіювання значень регістрів та констант в регістри.

Команди порівняння

Оператори рівності й відносин в мові C мають відповідні команди порівняння двох регістрів чи констант на мові асемблер Nios II.

Зсув та циклічний зсув

Для команд зсуву необхідно задати кількість біт константою або в регістрі.

Команди керування виконанням програми

Архітектура Nios II підтримує всі типи команд переходу: безумовні, умовні та виклики підпрограм. Умовні інструкції порівнюють значення регістрів безпосередньо та виконують перехід при виконанні умови. Всі ці команди не мають затримок виконання.

Інші команди керування

Ці операції включають в себе інструкцію перерви[уточнити], пастки[уточнити] та читання й запису в спеціальні регістри.

Користувацькі інструкції

Архітектура Nios II підтримує описані користувачем апаратні інструкції, використання яких відбувається так само, як і звичайних команд. Застосування апаратних користувацьких інструкцій виправдане у програмах, що інтенсивно працюють.[Що?] Команди обробки чисел з рухомою комою реалізовані як користувацькі і є додатковою частиною ядра. Базовий їх набір включає додавання, віднімання та множення з одинарною точністю, згідно стандарту IEEE 754–1985.

Нереалізовані команди

Деякі конфігурації процесора не підтримують весь набір інструкцій Nios II. У такому ядрі, операції без апаратної підтримки відомі як нереалізовані команди. При виклику такої команди процесор генерує виняткову ситуацію, обробник якої може викликати підпрограму, що емулює роботу в програмному забезпеченні. Таким чином, нереалізовані інструкції не впливають на програміста процесора.

Регістровий файл

Архітектура Nios II має регістровий файл, що складається з тридцяти двох 32-розрядних регістрів загального призначення, і до тридцяти двох 32-бітних регістрів керування. Архітектура підтримує два режими: адміністратора та користувача, що дозволяє коду системи захистити керуючі регістри від помилкових додатків.[Що?]

Процесор Nios II може мати до 63 наборів тіньових регістрів. Типове використання цих наборів полягає у прискоренні перемикання контексту. Коли тіньові регістрові набори реалізовані, процесор використовує дві спеціальні команди: rdprs та wrprs, що переміщують дані між регістрами. Реєстрацією тіньових наборів зазвичай піклується ядро операційної системи, вони прозорі для коду програми.

| Регістр | Назва | Призначення |

|---|---|---|

| r0 | zero | Завжди має нульовий вміст, запис будь-чого неможливий |

| r1 | at | Тимчасове зберігання даних асемблером |

| r2-r3 | Значення, що повертаються | |

| r4-r7 | Аргументи | |

| r8-r15 | Регістри загального призначення для коду, що викликає | |

| r16-r23 | Регістри загального призначення для коду, який викликається | |

| r24 | et | Тимчасове зберігання даних виняткової ситуації |

| r25 | bt | Тимчасове зберігання даних точки зупинки (для JTAG) |

| r26 | gp | Глобальний вказівник |

| r27 | sp | Вказівник стеку |

| r28 | fp | Вказівник фреймів |

| r29 | ea | Адреса повернення виняткової ситуації |

| r30 | ba | Адреса повернення точки зупинки |

| r31 | ra | Адреса повернення |

Див. також

Джерела

- Функції MMU — керування доступом до пам'яті, трансляція віртуальних адрес у фізичні, керування кешем[джерело?], захист сторінок пам'яті.