Мультизатворний польовий транзистор

Мультизатворний польовий транзистор (MuGFET) або мультизатворний MOSFET відноситься до МДН транзисторів (польовий транзистор метал-оксид-напівпровідник), який має більше одного затвора в одному пристрої. Кілька затворів можуть керуватись одним електродом затвора, в такому виконанні кілька поверхонь затвора діють як один затвор. Мулитизатворний польовий транзистор, що має виводи незалежних затворів, іноді називають польовим транзистором із незалежним мультизатвором (MIGFET). Найпоширенішими пристроями з мультизатворами є FinFET (польовий транзистор із вертикальним затвором) та GAAFET (польовий транзистор із затвором «увесь навколо» (gate-all-around field-effect transisto)), які є непланарними транзисторами, або 3D транзисторами .

Мультизатворні транзистори — один з декількох технологій, що розробляються виробниками напівпровідників МОН для створення все менших мікропроцесорів і комірок пам'яті, цей процес описується законом Мура[1]. Про потуги в розробці мультизатворних транзисторів повідомили Electrotechnical Laboratory, Toshiba, Grenoble INP, Hitachi, IBM, TSMC, UC Berkeley, Infineon Technologies, Intel, AMD, Samsung Electronics, KAIST, Freescale Semiconductor та інші. ITRS влучно спрогнозував, що такі пристрої будуть наріжним каменем технологій з техпроцесом меншим, ніж 32 nm. Основна перешкода широкому впровадженню — технологічність, оскільки як плоскі, так і непланарні структури представляють значні складнощі, особливо стосовно літографії та створення шаблонів. Інші допоміжні стратегії масштабування пристроїв включають техніку деформації каналів, технологію кремній на ізоляторі та матеріали затвора типу high-k-метал.

МДН транзистори (MOSFET) з подвійними затворами зазвичай використовуються в змішувачах ультракороткохвилового (УКХ) діапазону і у вихідних каскадах підсилювачів УКХ. Їх виготовляють такі виробники, як Motorola, NXP Semiconductors та Hitachi[2][3][4].

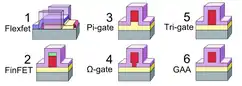

Типи

У літературі описуються десятки різноманітних варіантів мультизатворних транзисторів. Загалом, ці варіанти можуть бути диференційовані та класифіковані за архітектурою (планарний та 3D дизайн) та кількістю каналів/затворів (2, 3 або 4).

Планарний MOSFET з подвійним затвором (DGMOS)

Планарний МОП транзистор з подвійним затвором (DGMOS) виготовляється за звичайними «плоскими» технологіями (шар за шаром) аби уникнути більш жорстких вимог щодо літографії, як при виготовленні 3D структур. У планарних транзисторах з подвійним затвором канал стік-витік проходить між двома незалежно виготовленими затворами, що ізольовані від каналу оксидами. Основним завданням при виготовленні таких конструкцій є досягнення однакової висоти між верхнім та нижнім затвором[5].

Через 20 років після того, як MOSFET був вперше продемонстрований Мохамедом Аталлою та Доуном Кангом з Bell Labs в 1960 році[6] концепція MOSFET з подвійним затвором була запропонована Тошихіро Секігавою в патенті 1980 року, що описує планарний XMOS транзистор[7]. Секігава виготовив XMOS транзистор разом з Ютакою Хаяші в 1984 році. Вони продемонстрували, що ефект короткого каналу може бути значно зменшений за допомогою сендвічструктури з повністю виснаженого кремнію на ізоляторі (FDSOI) між двома затворами, з'єднаними між собою[8][9].

Це надихнуло Френсіса Балестра, Соріна Кристоловеану, М. Бенахіра та Тарека Елева на створення MOSFETу з подвійним затвором з використанням тонких плівок кремнію в 1987 році. Транзистори з подвійним затвором ефективно використовували кремнієву плівку (не тільки площу, а й об'єм) в сильній інверсії (Volume-Inversion MOSFET) або сильному накопиченні (Volume-Accumulation MOSFET). Цей спосіб побудови транзистора, демонстрував хороші електростатичні властивості та масштабованість мультизатворних пристроїв, показав високі електричні параметри транзисторів, особливо значне збільшення підпорогового нахилу, провідності та струму стоку. Для вивчення такого транзистора були використані програма моделювання та експерименти зі структурами SIMOX[10].

Секігава виготовив XMOS транзистор з довжиною затвору 2 мкм у 1987 році[7]. У 1988 році дослідницька група IBM на чолі з Біджаном Даварі виготовила 180 нм — 250 нм пристрої CMOS з подвійним затвором[11][12]. У 1992 році Секігава виготовив 380 нм пристрій XMOS. У 1998 році Е. Судзукі виготовив 40 нм пристрій XMOS. У дослідженнях і розробках польових транзисторів з подвійним затвором центр уваги поступово змістився від планарної технології, у напрямку до непланарних технологій FinFET (польовий транзистор з вертикальним затвором) та GAAFET (польовий транзистор із затвором типу «увесь навколо»).

FlexFET

FlexFET — це планарний транзистор із подвійним незалежним затвором, металевим верхнім затвором MOSFET та імплантованим JFET нижнім затвором, що розміщений у затворній траншеї. Цей пристрій має високу масштабованість, завдяки не імплантованим надмалим площадкам стоку та витоку; неепітаксійно утвореним стоку та витоку; і затвору, що утворюється в останню чергу. FlexFET — справжній транзистор з подвійним затвором, тому що (1) і верхній, і нижній затвор керують транзистором; і (2) робота затворів поєднана таким чином, що робота верхнього затвора впливає на роботу нижнього затвора і навпаки. FlexFET був розроблений і виробляється American Semiconductor, Inc.

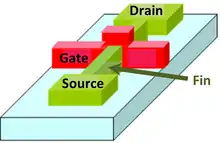

FinFET

FinFET (польовий транзистор із вертикальним затвором) — це тип непланарного транзистора, або «3D» транзистора (не плутати з 3D мікрочипами)[13]. FinFET — це варіація традиційних MOSFET, яка відрізняється наявністю тонкого інверсійного кремнієвого шару на каналі, що дозволяє затвору розділити канал на дві частини: ліву та праву сторони «плавника». Розмір «плавника» (вимірюється в напрямку від витоку до стоку) визначає ефективну довжину каналу пристрою. Структура затвору, що огортає канал, забезпечує кращий електричний контроль над каналом і, таким чином, допомагає зменшити струм витоку та подолати інші ефекти «короткого каналу».

Перший тип FinFET транзистора був названий «транзистор із збідненим спертим каналом» або «Дельта» транзистор, та вперше був виготовлений 1989 році[14][8][15] В кінці 1990 — х років, Діг Хісамото почав співпрацювати з міжнародною командою дослідників, що розвивали технології DELTA, включаючи TSMC і UC Berkeley. У 1998 році команда розробила перші N-канальні FinFET та успішно виготовила пристрої рівня 17 нм процесу. Наступного року вони розробили перші P-канальні FinFET[16]. У документі від грудня 2000 року вони ввели термін «FinFET» (польовий транзистор із вертикальним затвором)[17].

У поточному використанні термін FinFET має менш точне визначення. Виробники мікропроцесорів AMD, IBM і Freescale описують свої розробки пристроїв з подвійним затвором, як розробку FinFET[18], тоді як Intel уникає використання цього терміну при описі архітектури з потрійним затвором[19]. У технічній літературі термін FinFET використовується дещо загально, для опису будь-якої транзисторної архітектури на основі «плавника», незалежно від кількості затворів.

Перший 25-нанометровий транзистор, що працює всього від 0,7 В, був продемонстрований у грудні 2002 року TSMC. Конструкція «Omega FinFET», названа за схожістю між грецькою літерою «Омега» та формою, яку утворює затвор навколо структури стік — витік та має затримку затвора всього 0,39 пікосекунди (пс) для транзистора N-типу і 0,88 пс для транзистора P-типу.

У 2004 році компанія Samsung продемонструвала дизайн «Bulk FinFET», яка дала змогу масово виробляти пристрої FinFET. Вони продемонстрували динамічну пам'ять з довільним доступом (DRAM) 90 нм на об'ємному FinFET процесі.

У 2011 році Intel продемонструвала транзистори з потрійним затвором, де затвор огортає канал з трьох сторін, що дозволяє підвищити енергоефективність і зменшити затримку затвора, таким чином, збільшити продуктивність, випереджаючи планарні аналоги.

Комерційно виготовлені мікросхеми техпроцесу 22 нм і менше використовували конструкції затворів FinFET. Варіант «Tri-Gate» від Intel на 22 нм техпроцесі був оголошений в 2011 році для мікроархітектури Ivy Bridge. Ці пристрої постачаються з 2012 року.

У 2012 році Intel почала використовувати FinFET для своїх майбутніх комерційних пристроїв. Джерела припускають, що FinFET від Intel має незвичну форму трикутника, а не прямокутник, і припускається, що це тому, що трикутник має більшу структурну міцність і може бути надійніший у виготовленні, або тому, що трикутна призма має більшу площу поверхні на одиницю об'єму, ніж прямокутна призма, тим самим збільшуючи продуктивність комутації[20].

У вересні 2012 року GlobalFoundries оголосив про плани запропонувати в 2014 році 14-нанометрову технологію виготовлення тривимірних транзисторів FinFET[21]. Наступного місяця компанія конкурент TSMC оголосила про початок раннього або «ризикованого» виробництва 16 нм FinFETS у листопаді 2013 року[22].

У березні 2014 року TSMC оголосила, що наближається до впровадження декількох техпроцесів виготовлення 16-нм FinFET[23]:

- 16 нм FinFET (Q4 2014)

- 16 нм FinFET + (ІV квартал 2014 р.)

- 16 нм FinFET «Turbo» (за оцінками 2015—2016)

AMD випустила графічні процесори, використовуючи архітектуру чипів Polaris створених на 14 нм FinFET у червні 2016 року[24]. Компанія намагалася розробити дизайн, щоб забезпечити «покоління прориву в енергоефективності», пропонуючи також стабільну частоту кадрів для графіки, ігор, віртуальної реальності та мультимедійних додатків[25].

У березні 2017 року, Samsung і eSilicon оголосили про конвеєрне виробництво 14 нм FinFET ASIC в 2.5D корпусі[26][27].

Транзистор з потрійним затвором

Транзистор з потрійним затвором, також відомий як транзистор з трьома затворами — це тип MOSFET із затвором на трьох його сторонах[28]. Транзистор з потрійним затвором був вперше продемонстрований у 1987 році дослідницькою групою Toshiba. Вони зрозуміли, що повністю виснажений (FD fully depleted) кремнієвий канал сприяє поліпшенню перемикання завдяки зменшенню body-ефекту[29][30]. У 1992 році дослідник IBM Хон-Сум Вонг продемонстрував MOSFET з потрійним затвором[31].

Intel використовує непланарну технологію у виробництві транзисторів з потрійним затвором, що використовуються в процесорах Ivy Bridge, Haswell і Skylake . Ці транзистори використовують один затвор, розміщений зверху двох вертикальних затворів (суцільний затвор, огортає три сторони каналу), що дозволяє втричі збільшити площу поверхні для впливу електронів. Intel повідомляє, що їхні транзистори з потрійним затвором мають малий струм витоку і споживають набагато менше енергії, ніж прості транзистори. Це дозволяє до 37 % підвищити швидкість або зменшити потужність споживання на рівні 50 % від попереднього типу транзисторів, які використовує Intel[32].

Intel пояснює: «Поліпшене керування дозволяє збільшити струм транзистора, коли транзистор перебуває у відкритому стані (для продуктивності), і максимально наблизити його до нуля, коли він знаходиться в закритому стані (мінімізувати споживання) і дозволяє транзистору дуже швидко перемикатися між двома станами (знову ж таки, для продуктивності)»[33]. Intel заявила, що всі продукти виготовлені після Sandy Bridge будуть ґрунтуватися на цій розробці.

Intel оголосила про цю технологію у вересні 2002 року[34]. Intel анонсувала «транзистори з потрійним затвором», які максимально збільшують «продуктивність комутації транзисторів і зменшують витрату енергії». Через рік, у вересні 2003 року, AMD оголосила, що працює над подібними технологіями на Міжнародній конференції з твердотільних пристроїв та матеріалів[35]. Більше про цю технологію не було чути до оголошення Intel в травні 2011 року, хоча в IDF 2011 було заявлено, що вони демонстрували діючий чип SRAM на основі цієї технології 2009 року[36].

23 квітня 2012 року Intel випустила нову лінійку процесорів, що отримала назву Ivy Bridge, на якій є транзистори з потрійним затвором[37][38]. Intel працює над своєю архітектурою з 2002 року, але дата серійного виробництва 2011 рік. Нова архітектура транзистора була описана 4 травня 2011 року в Сан-Франциско[39]. Очікується, що фабрики Intel проведуть модернізацію протягом 2011 та 2012 років, щоб мати можливість виробляти процесори Ivy Bridge[40]. Окрім того, що вони будуть використовуватися в чипах Ivy Bridge від Intel для настільних ПК, нові транзистори також будуть використовуватися в мікросхемах Atom Intel для мобільних пристроїв.

Термін «потрійний затвор» іноді вживається як узагальнення для позначення будь-якого мультизатворного FET з трьома ефективними затворами або каналами.

Польовий транзистор із затвором типу «увесь навколо» (GAAFET)

Польовий транзистор із затвором типу «увесь навколо» (GAAFET — gate-all-around (GAA) FET), також відомий як (SGT — surrounding-gate transistor)[41][42], за концепцією схожий на FinFET, за винятком того, що затвор оточує область каналу з усіх сторін. Залежно від дизайну GAAFET можуть мати два або чотири ефективні затвори. Польові транзистори із затвором типу «увесь навколо» були успішно описані як теоретично, так і експериментально[43][44]. Також вони були успішно виготовлені на нанодротах InGaAs, які мають більш високу рухливість електронів, ніж кремній[45].

GAAFET був вперше продемонстрований у 1988 році дослідницькою командою Toshiba, яка продемонструвала вертикальний нанодріт GAAFET, який вони назвали «транзистором з затвором, що оточує» (SGT)[46][47][42]. Масуока, відомий як винахідник флеш-пам'яті, пізніше покинув Toshiba і заснував Unisantis Electronics у 2004 році для дослідження технологій затворів, що оточують разом з університетом Тохоку[48]. У 2006 році команда корейських дослідників з Корейського інституту науково-технічного розвитку (KAIST) та Національного центру нанотехнологій розробила 3 нм транзистор, найменший наноелектронний пристрій у світі, заснований на технології FinFET « увесь навколо» (GAA)[49][50].

Польовий транзистор з мультимостовим каналом (MBC) FET

Польовий транзистор з мультимостовим каналом (MBC) FET схожий на GAAFET за винятком використання наношарів замість нанопроводів[51].

Ринкова необхідність

Планарні транзистори вже кілька десятиліть є ядром інтегральних мікросхем, протягом яких розмір окремих транзисторів постійно зменшується. Зі зменшенням розміру планарні транзистори все частіше страждають від небажаних ефектів короткого каналу, струму витоку у закритому стані[52].

У мультизатворному транзисторі канал оточений кількома затворами на кількох поверхнях. Таким чином, він забезпечує кращий електричний контроль над каналом, що дозволяє більш ефективно зменшувати струм витоку в закритому стані. Також кілька затворів дозволяють збільшити струм у відкритому стані. Транзистори з мультизатвором також забезпечують кращу аналогову продуктивність за рахунок більшого коефіцієнту підсилення та кращого керування каналом по всій довжині[53]. Завдяки цьому ми спостерігаємо зниження енергоспоживання та підвищення продуктивності пристрою. Непланарні транзистори також є більш компактними, ніж звичайні плоскі, що забезпечує більш високу щільність транзисторів, що призводить до зменшення інтегральних схем.

Інтеграційні виклики

Основними проблемами інтеграції непланарних пристроїв з мультизатворами в звичайні процеси виробництва напівпровідників є:

- Виготовлення тонкого кремнієвого «плавника» в десятки нанометрів завширшки

- Виготовлення об'єднаних затворів на декількох сторонах «плавника»

Компактне моделювання

BSIMCMG106.0.0[54], офіційно представлений 1 березня 2012 року Каліфорнійським Університетом Berkeley BSIM Group, є першою стандартною моделлю для FinFET. BSIM-CMG реалізований у Verilog-A. Фізичні дані на основі поверхневого потенціалу отримані моделі як для внутрішніх, так і для зовнішніх шарів легованої речовини. Поверхневі потенціали на краях витоку та стоку розраховуються аналітично виходячи з сильнозбідненого матеріалу та квантово-механічного впливу. Ефект збагачення донорними домішками враховується використовуючи складніший підхід. Аналітичні рішення щодо поверхневого потенціалу тісно узгоджується з результатами 2D моделювання. Якщо концентрація донорних домішок є досить низькою, щоб ними нехтувати, обчислювальну ефективність можна підвищити, встановивши відповідну позначку (COREMOD = 1).

Ця модель враховує усі особливості поведінки мультизатворних транзисторів. Об'ємна інверсія врахована в рівнянні Пуассона. Аналіз електростатичного потенціалу в мультизатворних MOSFET породив рівняння для короткоканальних ефектів. Додатковий електростатичний контроль з бокових затворів (верхній-нижній затвор) (потрійний або квадрозатвор) також врахований у короткоканальній моделі.

Див. також

- Three-dimensional integrated circuit

- Semiconductor device

- Clock gating

- High-κ dielectric

- Next-generation lithography

- Extreme ultraviolet lithography

- Immersion lithography

- Strain engineering

- Very-large-scale integration (VLSI)

- Neuromorphic engineering

- Bit slicing

- 3D printing

- Silicon on insulator (SOI)

- MOSFET

- Floating-gate MOSFET

- Transistor

- BSIM

- High electron mobility transistor

- Field-effect transistor

- JFET

- Tetrode transistor

- Pentode transistor

- Memristor

- Quantum circuit

- Quantum gate

- Transistor model

- Die shrink

Джерела

- Risch, L. «Pushing CMOS Beyond the Roadmap», Proceedings of ESSCIRC, 2005, p. 63.

- 3N201 (Motorola) - Dual Gate Mosfet Vhf Amplifier. Doc.chipfind.ru. Процитовано 10 березня 2014.

- 3SK45 datasheet pdf datenblatt - Hitachi Semiconductor - SILICON N-CHANNEL DUAL GATE MOSFET. Alldatasheet.com. Процитовано 10 березня 2014.

- BF1217WR. Процитовано 10 травня 2015.

- Wong, H-S.; Chan, K.; Taur, Y. (10 грудня 1997). Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel. Electron Devices Meeting, 1997. IEDM '97. Technical Digest. с. 427–430. ISBN 978-0-7803-4100-5. ISSN 0163-1918. doi:10.1109/IEDM.1997.650416.

- 1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated. The Silicon Engine. Computer History Museum. Процитовано 25 вересня 2019.

- Koike, Hanpei; Nakagawa, Tadashi; Sekigawa, Toshiro; Suzuki, E.; Tsutsumi, Toshiyuki (23 лютого 2003). Primary Consideration on Compact Modeling of DG MOSFETs with Four-terminal Operation Mode. TechConnect Briefs 2 (2003): 330–333.

- Colinge, J.P. (2008). FinFETs and Other Multi-Gate Transistors. Springer Science & Business Media. с. 11 & 39. ISBN 9780387717517.

- Sekigawa, Toshihiro; Hayashi, Yutaka (August 1984). Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate. Solid-State Electronics 27 (8): 827–828. Bibcode:1984SSEle..27..827S. ISSN 0038-1101. doi:10.1016/0038-1101(84)90036-4.

- Balestra, Francis; Cristoloveanu, Sorin; Benachir, M.; Elewa, Tarek; Brini, Jean (September 1987). Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance. IEEE Electron Device Letters 8 (9): 410–412. Bibcode:1987IEDL....8..410B. ISSN 0741-3106. doi:10.1109/EDL.1987.26677.

- Davari, Bijan; Chang, Wen-Hsing; Wordeman, Matthew R.; Oh, C. S.; Taur, Yuan; Petrillo, Karen E.; Rodriguez, M. D. (December 1988). A high performance 0.25 mu m CMOS technology. Technical Digest., International Electron Devices Meeting: 56–59. doi:10.1109/IEDM.1988.32749.

- Davari, Bijan; Wong, C. Y.; Sun, Jack Yuan-Chen; Taur, Yuan (December 1988). Doping of n/sup +/ and p/sup +/ polysilicon in a dual-gate CMOS process. Technical Digest., International Electron Devices Meeting: 238–241. doi:10.1109/IEDM.1988.32800.

- What is Finfet?. Computer Hope. 26 квітня 2017. Процитовано 4 липня 2019.

- IEEE Andrew S. Grove Award Recipients. IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Процитовано 4 липня 2019.

- Hisamoto, D.; Kaga, T.; Kawamoto, Y.; Takeda, E. (December 1989). A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET. International Technical Digest on Electron Devices Meeting: 833–836. doi:10.1109/IEDM.1989.74182.

- Tsu‐Jae King, Liu (11 червня 2012). FinFET: History, Fundamentals and Future. University of California, Berkeley. Symposium on VLSI Technology Short Course. Процитовано 9 липня 2019.

- Hisamoto, Digh; Hu, Chenming; Bokor, J.; King, Tsu-Jae; Anderson, E. та ін. (December 2000). FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Transactions on Electron Devices 47 (12): 2320–2325. Bibcode:2000ITED...47.2320H. doi:10.1109/16.887014. Проігноровано невідомий параметр

|citeseerx=(довідка) - AMD Newsroom. Amd.com. 10 вересня 2002. Архів оригіналу за 13 травня 2010. Процитовано 7 липня 2015.

- Intel Silicon Technology Innovations. Intel.com. Архів оригіналу за September 3, 2011. Процитовано 10 березня 2014.

- Intel's FinFETs are less fin and more triangle. EE Times. Процитовано 10 березня 2014.

- Globalfoundries looks leapfrog fab rivals with new process. EE Times. Процитовано 10 березня 2014.

- TSMC taps ARM's V8 on road to 16 nm FinFET. EE Times. Процитовано 10 березня 2014.

- TSMC likely to launch 16 nm FinFET+ process at year-end 2014, and "FinFET Turbo" later in 2015-16. DIGITIMES. Процитовано 31 березня 2014.

- Smith, Ryan. The AMD Radeon RX 480 Preview: Polaris Makes Its Mainstream Mark. Процитовано 3 червня 2018.

- AMD Demonstrates Revolutionary 14nm FinFET Polaris GPU Architecture. AMD. Процитовано 4 січня 2016.

- High-performance, high-bandwidth IP platform for Samsung 14LPP process technology. 22 березня 2017.

- Samsung and eSilicon Taped Out 14nm Network Processor with Rambus 28G SerDes Solution. 22 березня 2017.

- Colinge, J.P. (2008). FinFETs and Other Multi-Gate Transistors. Springer Science & Business Media. с. 12. ISBN 9780387717517.

- Hieda, K.; Horiguchi, Fumio; Watanabe, H.; Sunouchi, Kazumasa; Inoue, I.; Hamamoto, Takeshi (December 1987). New effects of trench isolated transistor using side-wall gates. 1987 International Electron Devices Meeting: 736–739. doi:10.1109/IEDM.1987.191536.

- Brozek, Tomasz (2017). Micro- and Nanoelectronics: Emerging Device Challenges and Solutions. CRC Press. с. 116–7. ISBN 9781351831345.

- Wong, Hon-Sum (December 1992). Gate-current injection and surface impact ionization in MOSFET's with a gate induced virtual drain. 1992 International Technical Digest on Electron Devices Meeting: 151–154. ISBN 0-7803-0817-4. doi:10.1109/IEDM.1992.307330.

- Cartwright J. (2011). Intel enters the third dimension. Nature. doi:10.1038/news.2011.274. Процитовано 10 травня 2015.

- Below 22nm, spacers get unconventional: Interview with ASM. ELECTROIQ. Процитовано 4 травня 2011.

- High Performance Non-Planar Tri-gate Transistor Architecture; Dr. Gerald Marcyk. Intel, 2002

- AMD Details Its Triple-Gate Transistors. Xbitlabs.com. Архів оригіналу за 10 березня 2014. Процитовано 10 березня 2014.

- IDF 2011: Intel Looks to Take a Bite Out of ARM, AMD With 3D FinFET Tech. DailyTech. Архів оригіналу за 10 березня 2014. Процитовано 10 березня 2014.

- Miller, Michael J. Intel Releases Ivy Bridge: First Processor with "Tri-Gate" Transistor. PC Magazine.

- Intel Reinvents Transistors Using New 3-D Structure. Intel. Процитовано 5 квітня 2011.

- Transistors go 3D as Intel re-invents the microchip. Ars Technica. 5 травня 2011. Процитовано 7 травня 2011.

- Murray, Matthew (4 травня 2011). Intel's New Tri-Gate Ivy Bridge Transistors: 9 Things You Need to Know. PC Magazine. Процитовано 7 травня 2011.

- Claeys, C.; Murota, J.; Tao, M.; Iwai, H.; Deleonibus, S. (2015). ULSI Process Integration 9. The Electrochemical Society. с. 109. ISBN 9781607686750.

- Ishikawa, Fumitaro; Buyanova, Irina (2017). Novel Compound Semiconductor Nanowires: Materials, Devices, and Applications. CRC Press. с. 457. ISBN 9781315340722.

- Singh, N.; Agarwal, A.; Bera, L. K.; Liow, T. Y.; Yang, R.; Rustagi, S. C.; Tung, C. H.; Kumar, R. та ін. (2006). High-Performance fully depleted Silicon Nanowire Gate-All-Around CMOS devices. IEEE Electron Device Letters 27 (5): 383–386. Bibcode:2006IEDL...27..383S. ISSN 0741-3106. doi:10.1109/LED.2006.873381.

- Dastjerdy, E.; Ghayour, R.; Sarvari, H. (August 2012). Simulation and analysis of the frequency performance of a new silicon nanowire MOSFET structure. Physica E 45: 66–71. Bibcode:2012PhyE...45...66D. doi:10.1016/j.physe.2012.07.007.

- Gu, J. J.; Liu, Y. Q.; Wu, Y. Q.; Colby, R.; Gordon, R. G.; Ye, P. D. (December 2011). First Experimental Demonstration of Gate-all-around III-V MOSFETs by Top-down Approach. 2011 International Electron Devices Meeting: 33.2.1–33.2.4. Bibcode:2011arXiv1112.3573G. arXiv:1112.3573. doi:10.1109/IEDM.2011.6131662. Процитовано 10 травня 2015.

- Masuoka, Fujio; Takato, Hiroshi; Sunouchi, Kazumasa; Okabe, N.; Nitayama, Akihiro; Hieda, K.; Horiguchi, Fumio (December 1988). High performance CMOS surrounding-gate transistor (SGT) for ultra high density LSIs. Technical Digest., International Electron Devices Meeting: 222–225. doi:10.1109/IEDM.1988.32796.

- Brozek, Tomasz (2017). Micro- and Nanoelectronics: Emerging Device Challenges and Solutions. CRC Press. с. 117. ISBN 9781351831345.

- Company Profile. Unisantis Electronics. Архів оригіналу за 22 лютого 2007. Процитовано 17 липня 2019.

- Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology ). Nanoparticle News. 1 квітня 2006. Архів оригіналу за 6 November 2012.

- Lee, Hyunjin (2006). Sub-5nm All-Around Gate FinFET for Ultimate Scaling. Symposium on VLSI Technology, 2006: 58–59. ISBN 978-1-4244-0005-8. doi:10.1109/VLSIT.2006.1705215.

- Cutress, Ian. Samsung Announces 3nm GAA MBCFET PDK, Version 0.1. www.anandtech.com.

- Subramanian V (2010). Multiple gate field-effect transistors for future CMOS technologies. IETE Technical Review 27 (6): 446–454. doi:10.4103/0256-4602.72582. Архів оригіналу за 23 березня 2012.

- Subramanian (5 грудня 2005). Device and circuit-level analog performance trade-offs: a comparative study of planar bulk FETs versus FinFETs. Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International: 898–901.

- BSIMCMG Model. UC Berkeley. Архів оригіналу за 21 липня 2012.